**COURSE FILE**

NAME OF THE STAFF

:DEEPA .S.R

**SUBJECT CODE/NAME**

SEMESTER/YEAR

ACADEMIC YEAR

BRANCH

:18CS34/COMPUTER ORGANIZATION

: III Sem/II Year A Section

: 2020-21

**:COMPUTER SCIENCE & ENGINEERING**

deepa **FACULTY IN-CHARGE**

, ulcal-apm

HOD Head of the Department Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

# **K.S. INSTITUTE OF TECHNOLOGY**

DEPARTMENT OF COMPUTER SCIENCE ENGINEERING

### Vision of the Institute

To impart quality technical education with ethical values, employable skills and research to achieve excellence

# **Mission of the Institute**

- To attract and retain highly qualified, experienced & committed faculty.

- To create relevant infrastructure.

- Network with industry & premier institutions to encourage emergence of new ideas by providing research & development facilities to strive for academic excellence.

• To inculcate the professional & ethical values among young students with employable skills & knowledge acquired to transform the society.

### Vision of the Department

To create competent professionals in Computer Science and Engineering with adequate skills to drive the IT industry

### **Mission of the Department**

- Impart sound technical knowledge and quest for continuous learning.

- To equip students to furnish Computer Applications for the society through experiential learning and research with professional ethics.

- Encourage team work through inter-disciplinary project and evolve as leaders with social concerns.

Dept. of Computer Science & Engy K.S. Institute of Technology Bengaluru -560 109

# **K.S. INSTITUTE OF TECHNOLOGY**

DEPARTMENT OF COMPUTER SCIENCE ENGINEERING

### **Program Educational Objectives**

- **PEO1:** Excel in professional career by acquiring knowledge in cutting edge technology and contribute to the society as an excellent employee or as an entrepreneur in the field of Computer Science & Engineering.

- **PEO2:** Continuously enhance their knowledge on par with the development in IT industry and pursue higher studies in Computer Science & Engineering.

- **PEO3:** Exhibit professionalism, cultural awareness, team work, ethics, and effective communication skills with their knowledge in solving social and environmental problems by applying computer technology.

# **Program Specific Outcomes (PSO)**

- **PSO1:** Ability to understand, analyze problems and implement solutions in programming languages, as well to apply concepts in core areas of Computer Science in association with professional bodies and clubs.

- **PSO2:** Ability to use computational skills and apply software knowledge to develop effective solutions and data to address real world challenges.

Head of the Department Dept. of Computer Science & Engg K.S. Institute of Technology

# **K.S. INSTITUTE OF TECHNOLOGY**

**DEPARTMENT OF COMPUTER SCIENCE ENGINEERING**

### **Program Outcomes**

- **PO1:** Engineering knowledge: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- **PO2: Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- **PO3:** Design/development of solutions: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- **PO4:** Conduct investigations of complex problems: Use researchbased knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- **PO5:** Modern tool usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- **PO6:** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- **PO7:** Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- **PO8:** Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **PO9:** Individual and team work: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- **PO10:** Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- **PO11: Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- **PO12:** Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

) Made up M

Head of the Department Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

# **K. S. INSTITUTE OF TECHNOLOGY**

#14, Raghuvanahalli, Kanakapura Main Road, Bengaluru-5600109

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

| Course: C                                                                    | OMPUTER                                                                                 | ORGANIZ                                                                             | ATION                                                                                                      |                                                |                                                |                          |                                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|--------------------------|----------------------------------|

| Type: Core                                                                   | •                                                                                       |                                                                                     | Course Code:                                                                                               | 18CS34                                         | Academi                                        | c Year                   | ::2020-21                        |

| Name: Dee                                                                    | pa .S.R                                                                                 |                                                                                     |                                                                                                            |                                                | Sem & S                                        | ec: III                  | Α                                |

|                                                                              |                                                                                         |                                                                                     | No of Hours pe                                                                                             | er week                                        | 1                                              |                          |                                  |

| The<br>(Lecture                                                              |                                                                                         |                                                                                     | ical/Field<br>lied Activities                                                                              | Tot                                            | al/Week                                        | Tot                      | tal teaching hours               |

| 4                                                                            |                                                                                         |                                                                                     | 0                                                                                                          |                                                | 4                                              |                          | 40                               |

|                                                                              |                                                                                         |                                                                                     | Marks                                                                                                      |                                                |                                                |                          |                                  |

|                                                                              | Assessment                                                                              |                                                                                     | Examination                                                                                                |                                                | Total                                          |                          | Credits                          |

|                                                                              | 40<br>tive of the (                                                                     |                                                                                     | 60                                                                                                         |                                                | 100                                            |                          | 3                                |

| <ul> <li>Exp<br/>oper<br/>inst</li> <li>Den<br/>inte</li> <li>Des</li> </ul> | ration. Illu<br>ructions.<br>nonstrate d<br>rfaces. Dese<br>cribe arithm<br>earning Out | sic sub sys<br>istrate the<br>ifferent way<br>cribe memo<br>netic and lo<br>tcomes: | tems of a com<br>concept of<br>ys of communic<br>ory hierarchy ar<br>ogical operation<br>adents will be ab | program<br>ating wit<br>id concep<br>s with in | s as seque<br>th I/O device<br>ot of virtual n | nces<br>s and s<br>nemor | of machine<br>standard I/O<br>y. |

| CO#                                                                          |                                                                                         | C                                                                                   | COURSE OUT                                                                                                 | COMES                                          |                                                |                          | K-LEVEL                          |

| 18CS34.1                                                                     |                                                                                         |                                                                                     | re & organizati<br>formats and add                                                                         |                                                | -                                              | em,                      | Applying<br>(K3)                 |

| 18CS34.2                                                                     |                                                                                         |                                                                                     | I/O communica<br>apt service rout                                                                          |                                                | n standard bu                                  | 15                       | Applying<br>(K3)                 |

| 18CS34.3                                                                     | Identify d                                                                              | ifferent me                                                                         | mories and me                                                                                              | mory ma                                        | pping techni                                   | ques.                    | Applying<br>(K3)                 |

| 18CS34.4                                                                     | Design dif                                                                              | fferent Arit                                                                        | hmetic operatio                                                                                            | onal units                                     | 5.                                             |                          | Applying<br>(K3)                 |

| 18CS34.5                                                                 | Derive control sequences for hardwired and micro-program                                                                                                                                                                                                                                                                                                                                                                              | oplying<br>(K3)                                       |  |  |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Module 1                                                                 | Syllabus Content:                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |  |  |  |  |

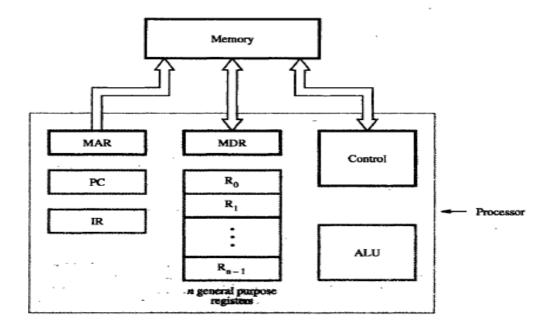

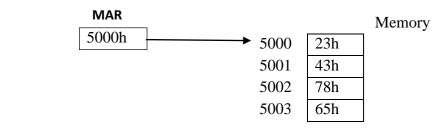

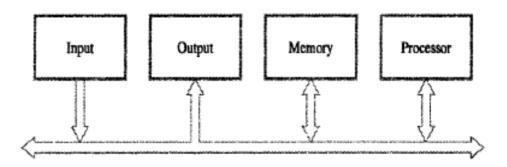

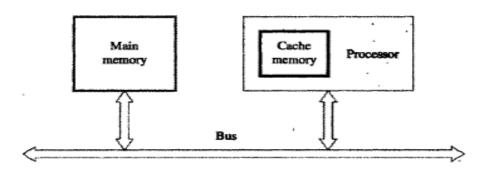

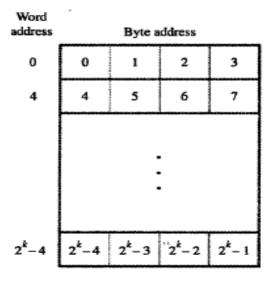

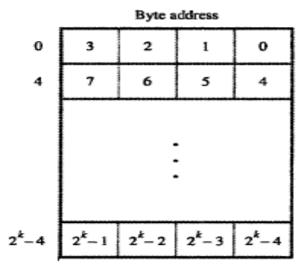

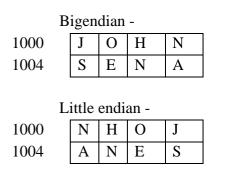

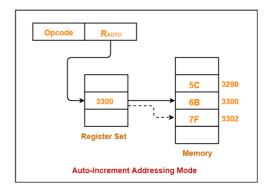

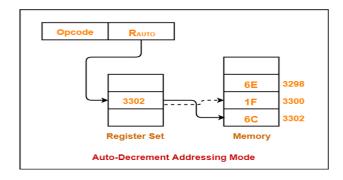

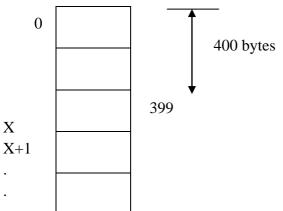

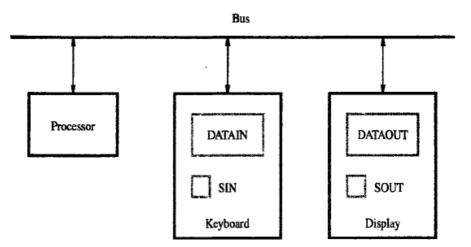

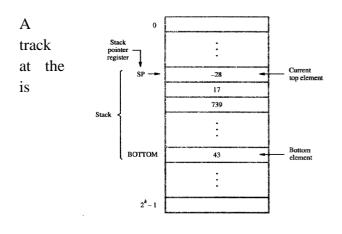

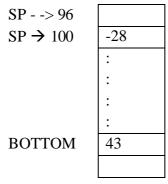

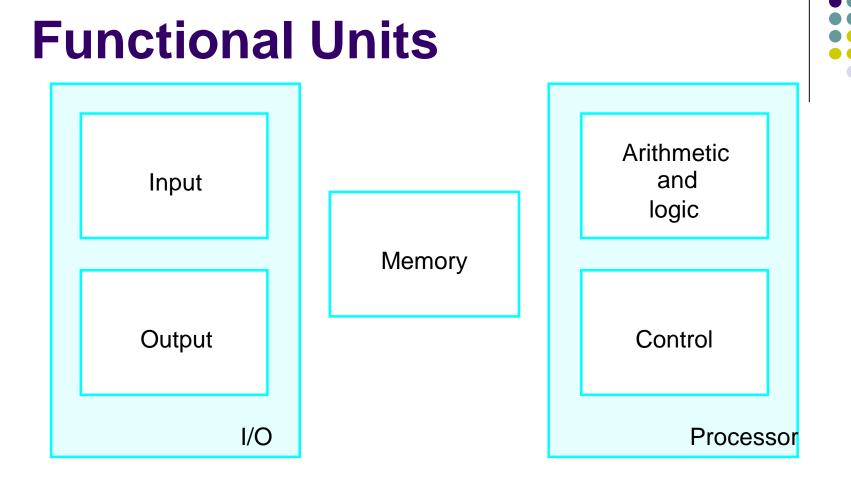

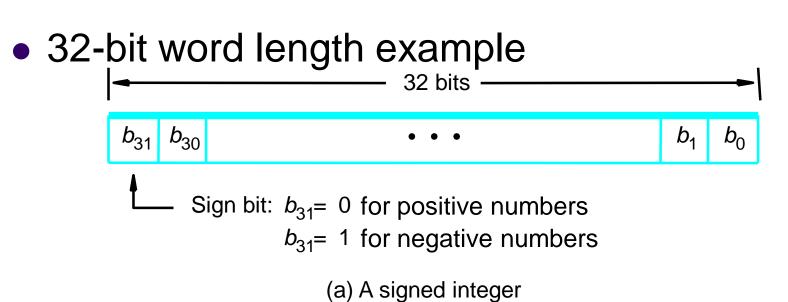

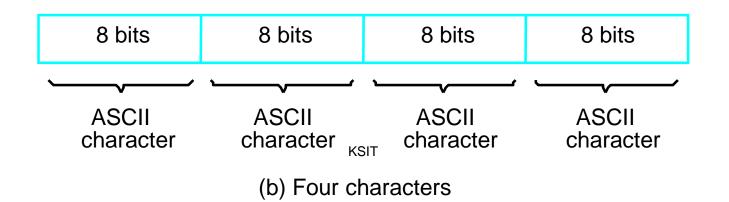

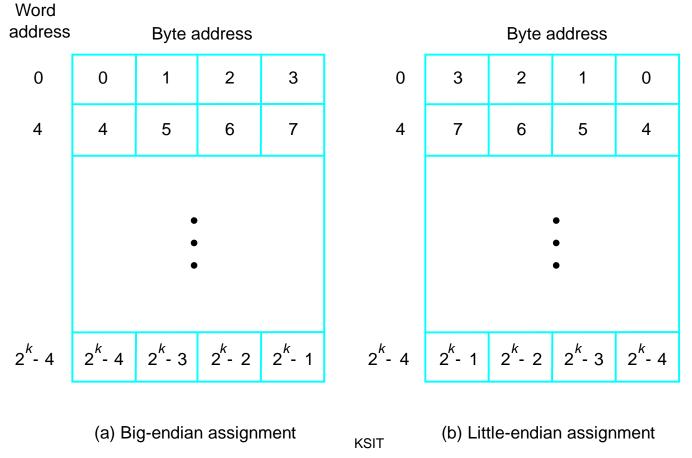

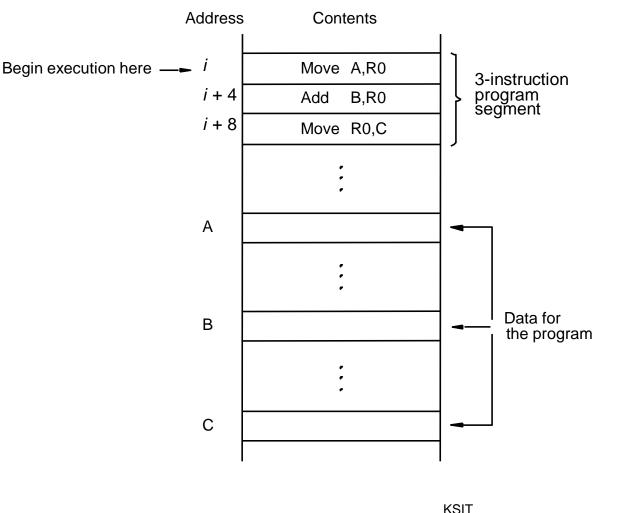

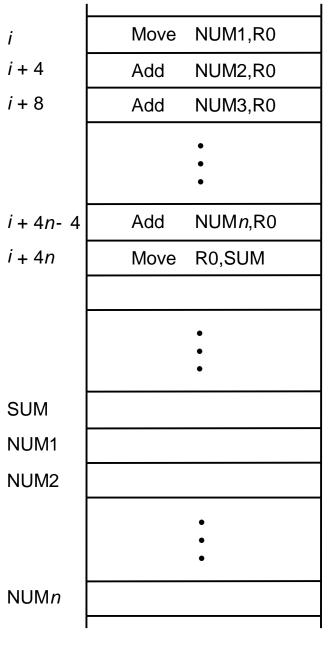

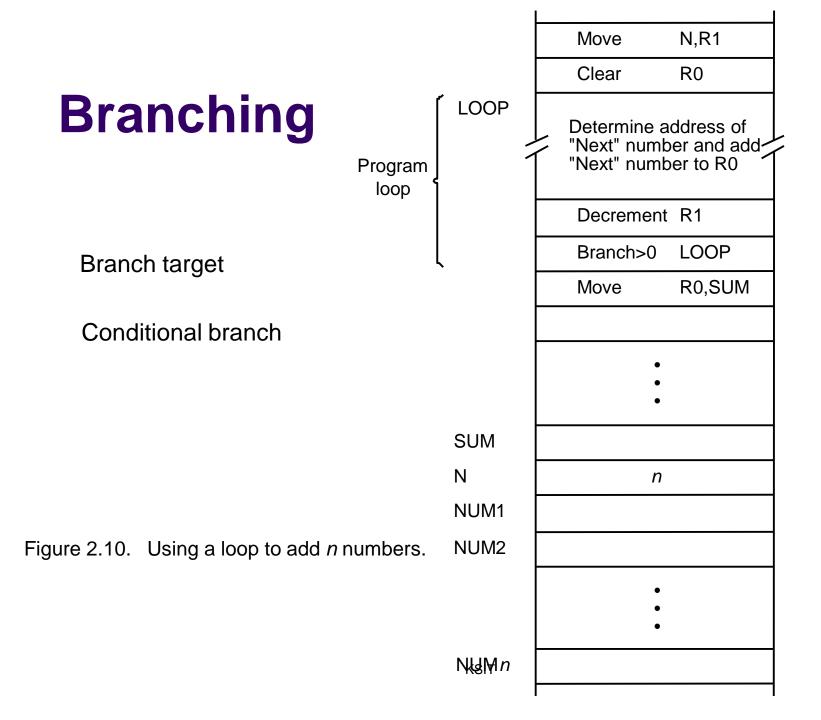

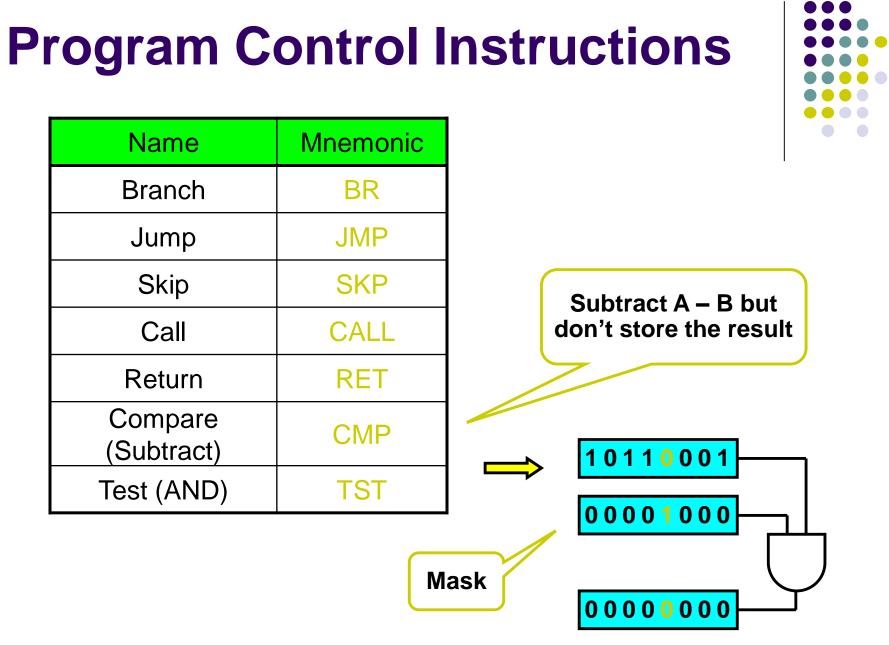

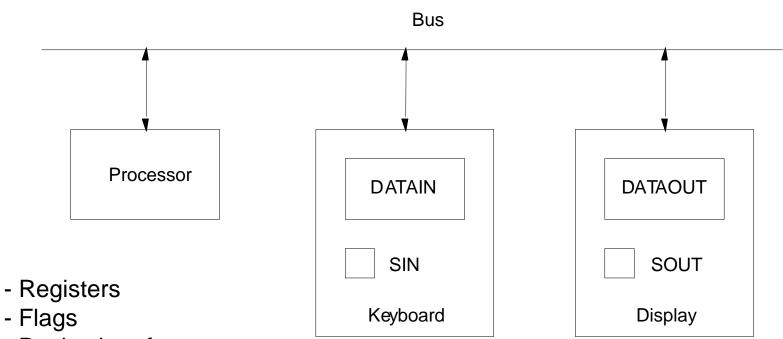

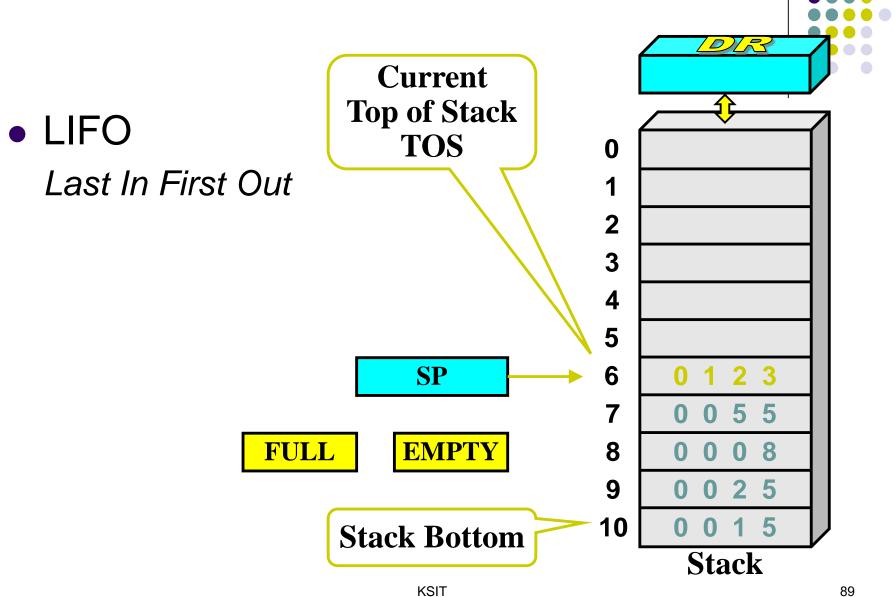

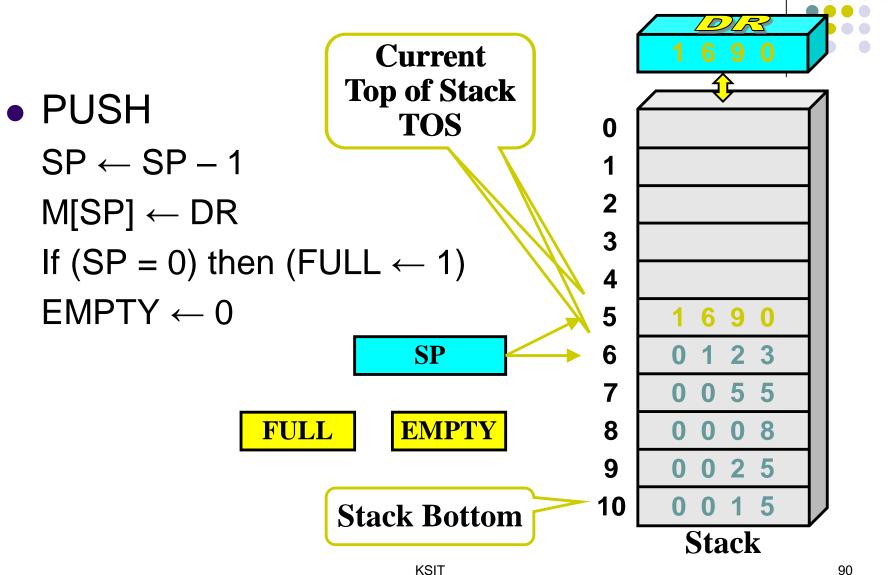

| Performanc<br>Measureme<br><b>Machine In</b><br>Operations,<br>Language, | <b>Acture of Computers:</b> Basic Operational Concepts, Bus Structures,<br>be – Processor Clock, Basic Performance Equation, Clock Rate, Performance<br>ent.<br><b>Astructions and Programs:</b> Memory Location and Addresses, Memory<br>Instructions and Instruction Sequencing, Addressing Modes, Assembly<br>Basic Input and Output Operations, Stacks and Queues, Subroutines,<br>Instructions, Encoding of Machine Instructions | <b>CO1</b><br><b>8 hrs</b><br>PO1-3<br>PO2-2<br>PO3-2 |  |  |  |  |

| <ol> <li>Explana</li> <li>Illust</li> <li>basic</li> </ol>               | nd of this session the student will be able to,<br>ain the structure of computer, organizational structure and operation<br>trate the concept of programs as sequences of machine instructions and<br>c I/O operations<br>erstand addressing modes, stacks and queues.                                                                                                                                                                | PS01-3<br>PS02-2                                      |  |  |  |  |

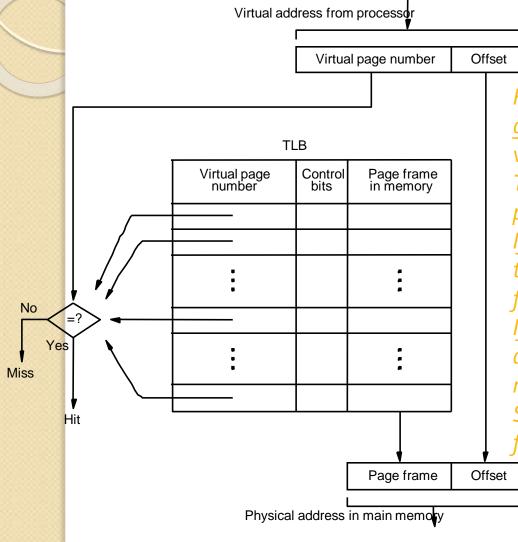

| <u>Module 2</u><br>Input/Outp                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                       | CO2<br>8 hrs.                                         |  |  |  |  |

|                                                                          | SB.<br>nd of this session the student will be able to,<br>Demonstrate different ways of communicating with I/O devices                                                                                                                                                                                                                                                                                                                | P01-3<br>P02-2<br>P03-2<br>PS01-3                     |  |  |  |  |

| 2. U                                                                     | Inderstand standard I/O Interfaces                                                                                                                                                                                                                                                                                                                                                                                                    | PS02-2                                                |  |  |  |  |

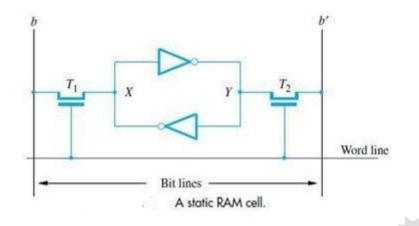

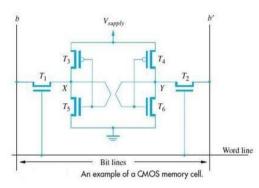

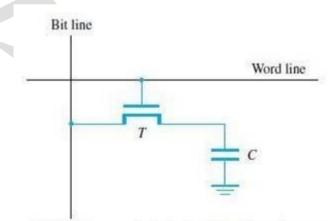

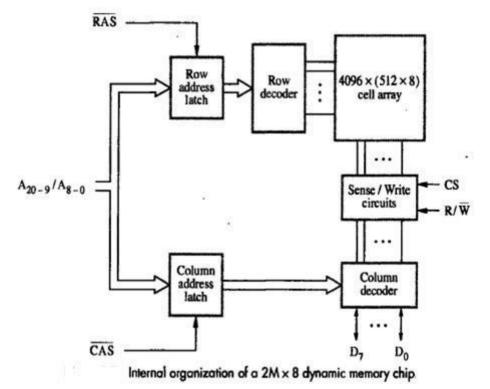

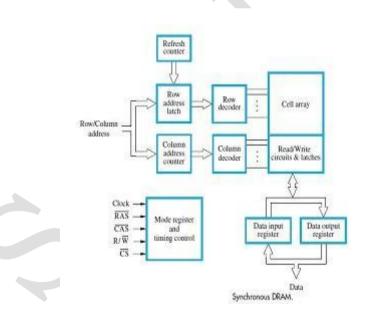

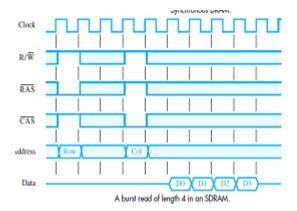

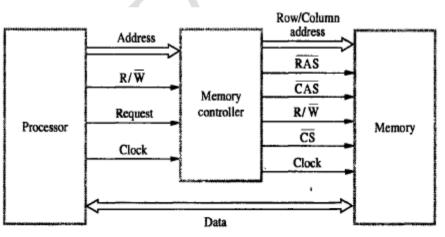

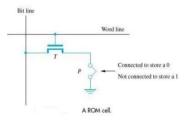

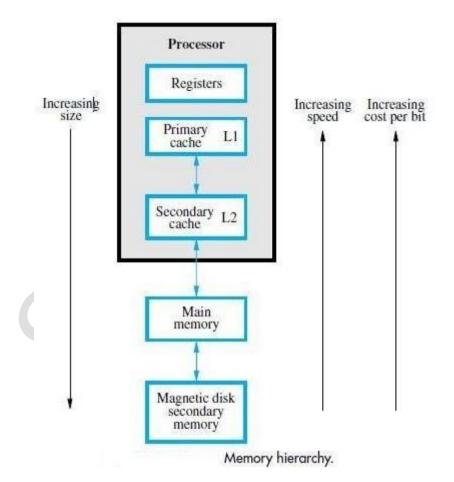

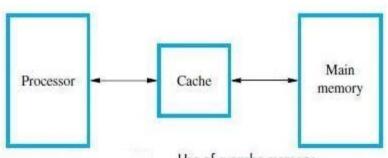

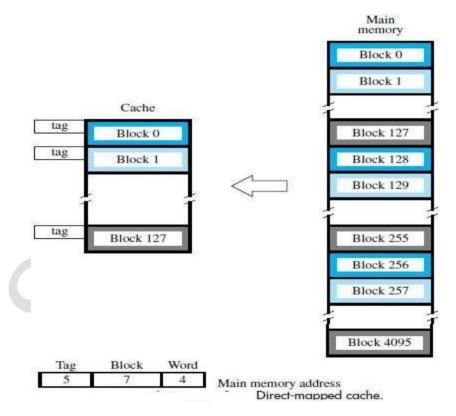

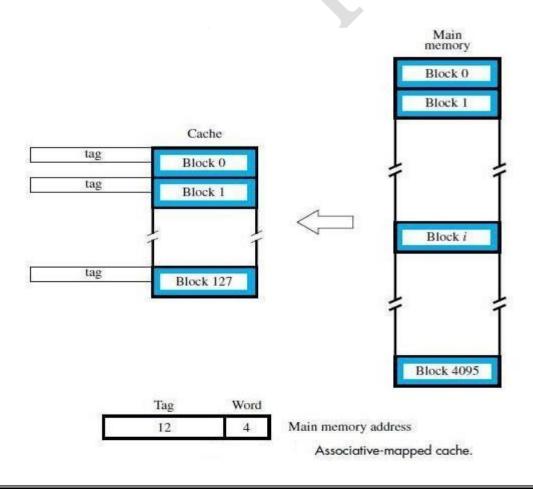

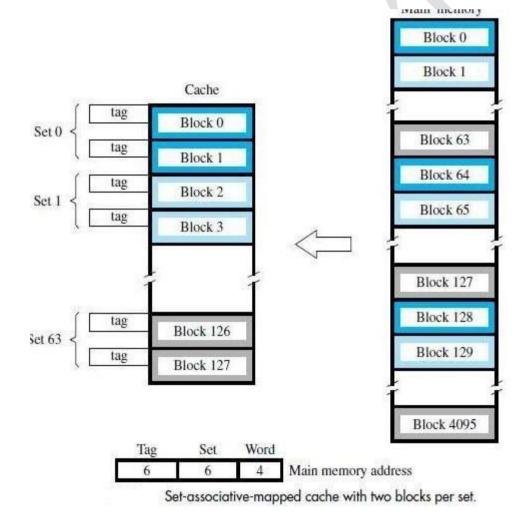

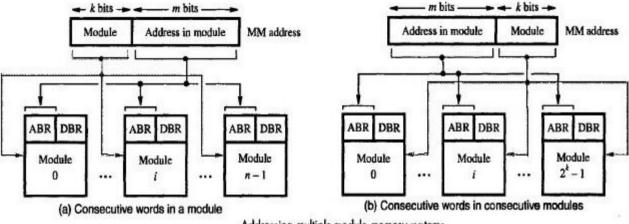

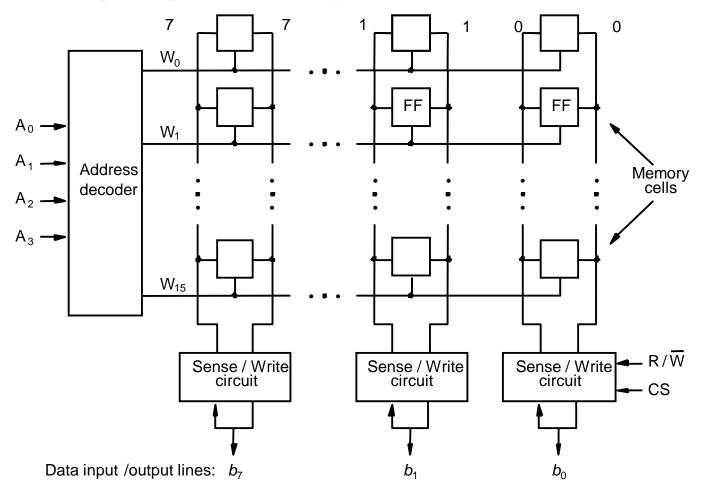

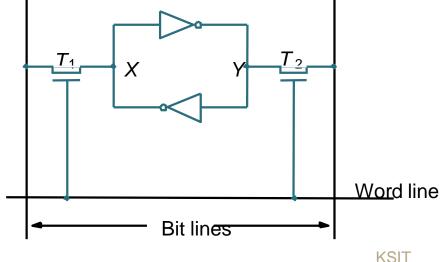

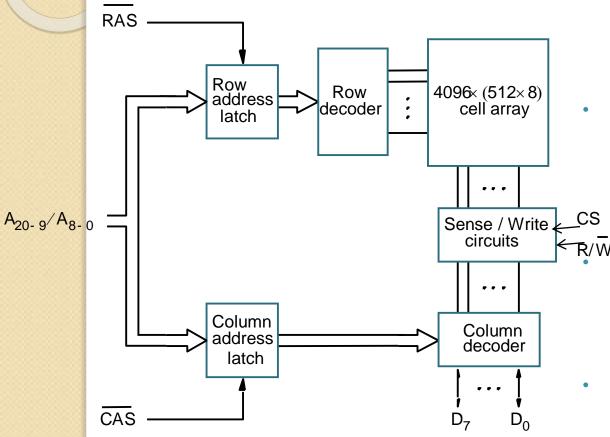

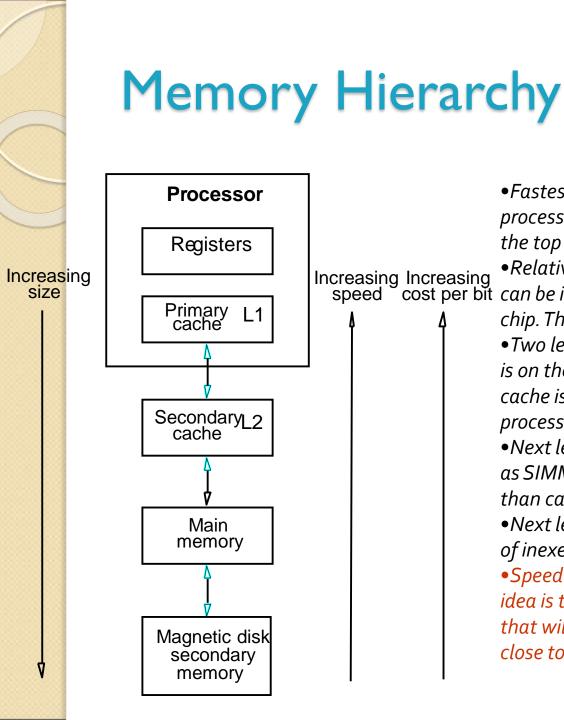

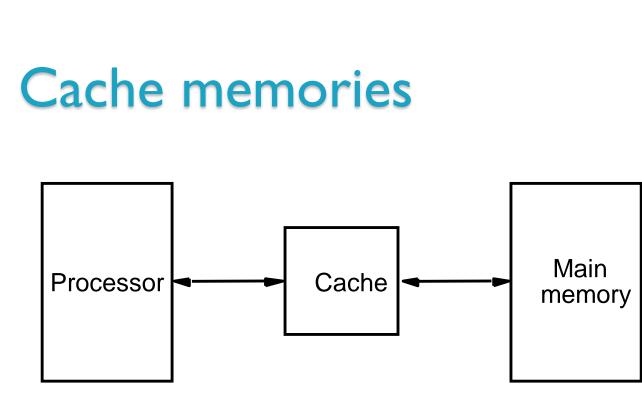

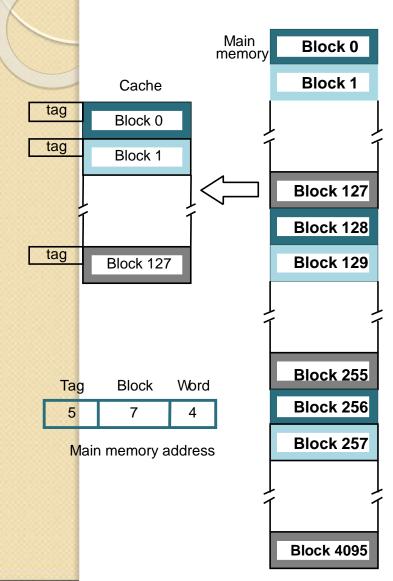

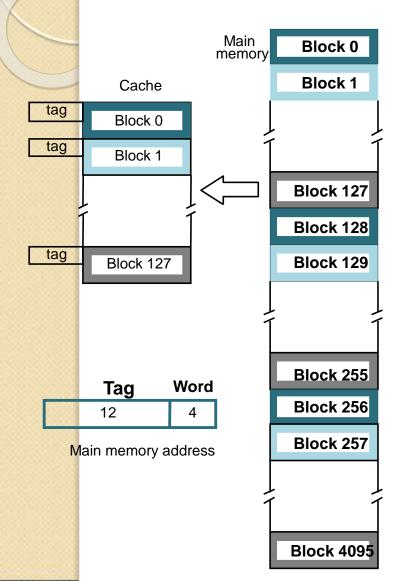

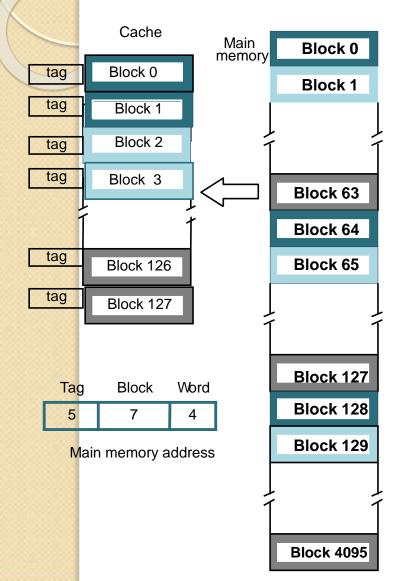

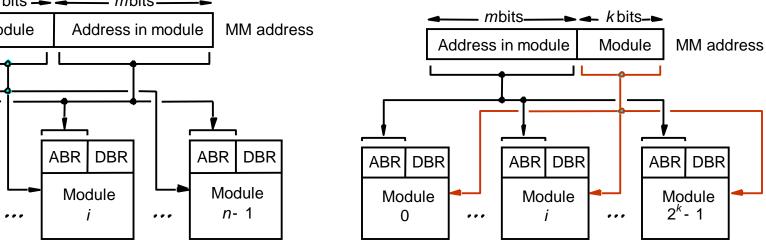

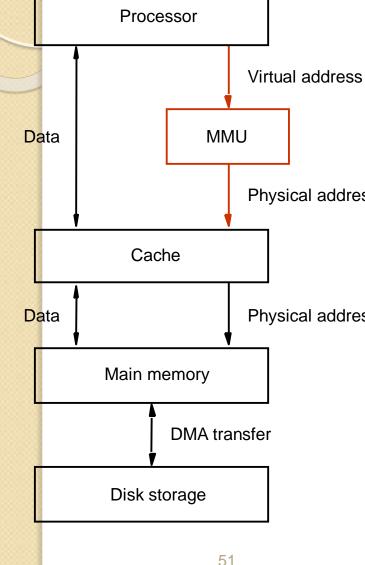

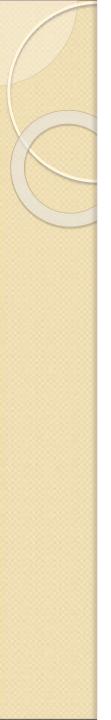

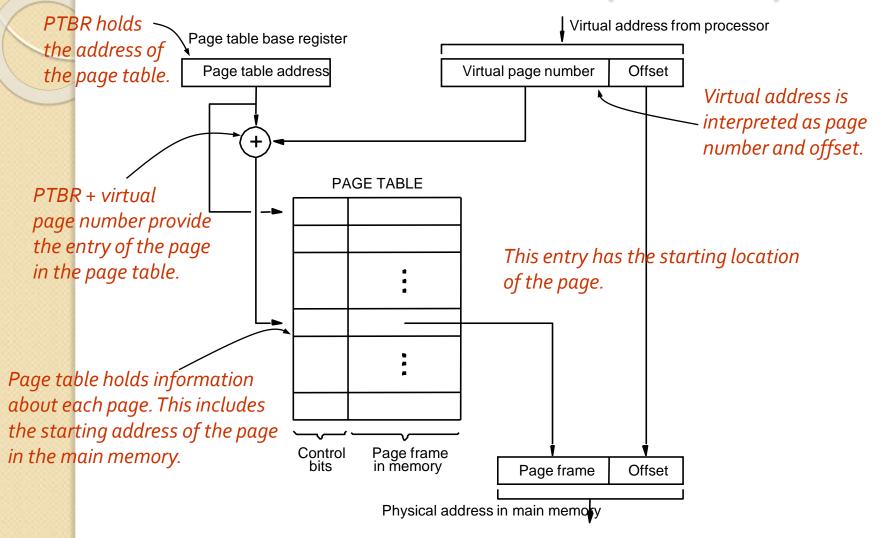

| Memories,                                                                | <b>System:</b> Basic Concepts, Semiconductor RAM Memories, Read Only Speed, Size and Cost, Cache Memories – Mapping Functions and the Considerations.                                                                                                                                                                                                                                                                                 | CO3<br>8 hrs                                          |  |  |  |  |

| 1. D<br>2. C                                                             | nd of this session the student will be able to,<br>Describe memory hierarchy<br>Compare different types of memories<br>Explain the concept of virtual memory                                                                                                                                                                                                                                                                          | P01-3<br>P02-2<br>P03-3<br>PS01-3<br>PS02-2           |  |  |  |  |

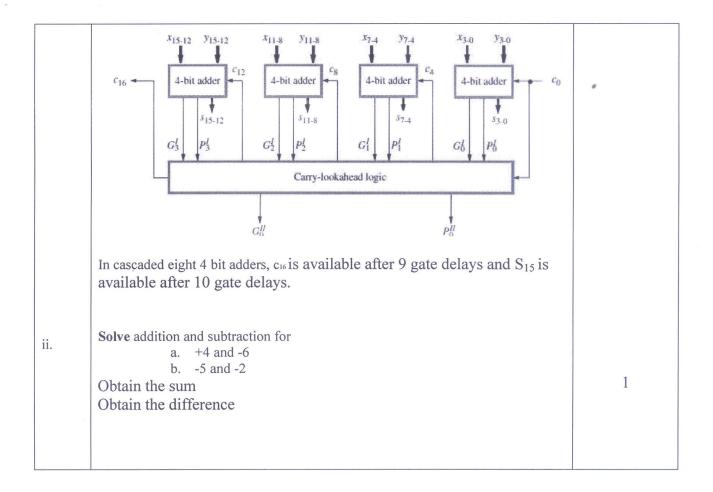

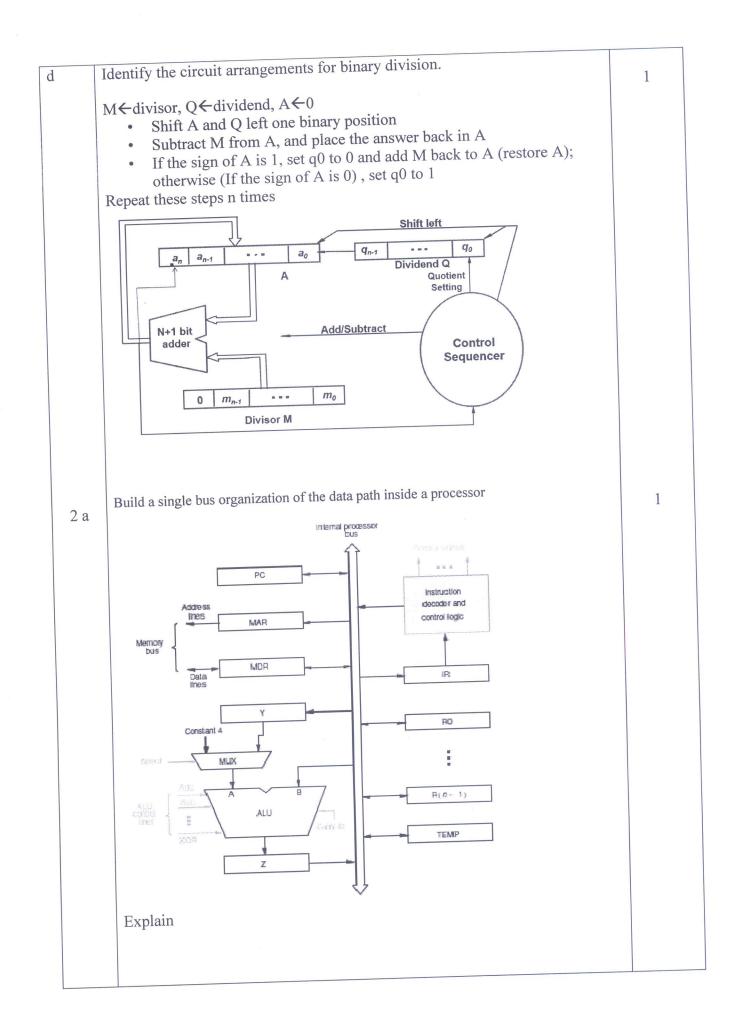

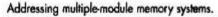

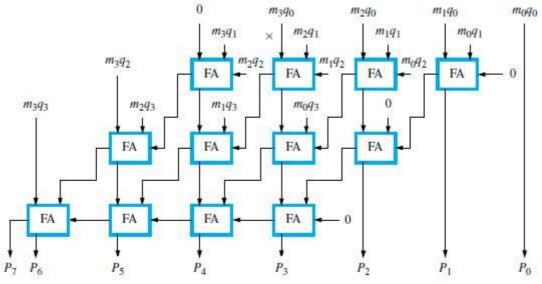

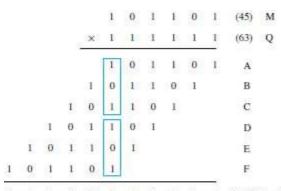

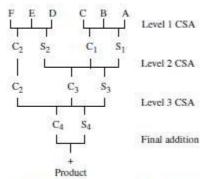

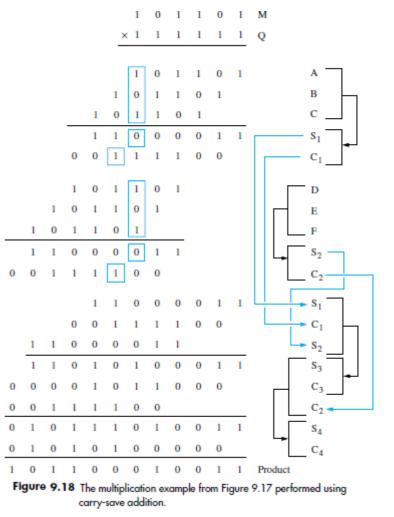

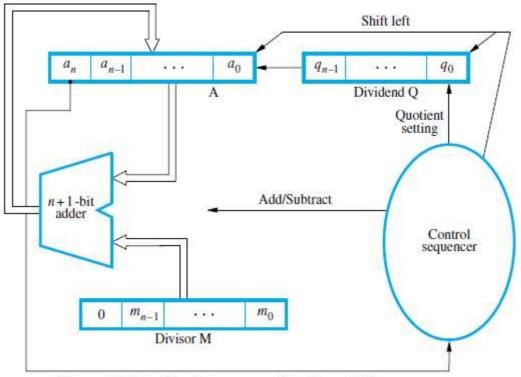

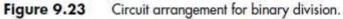

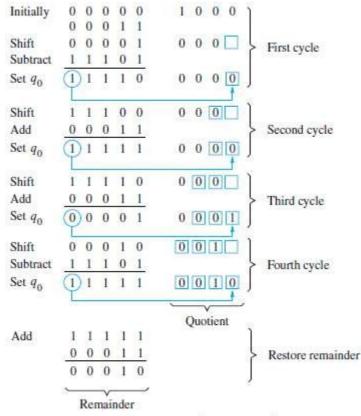

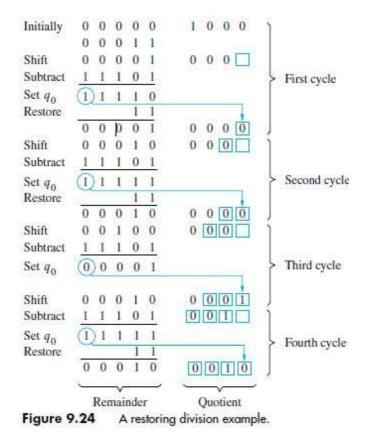

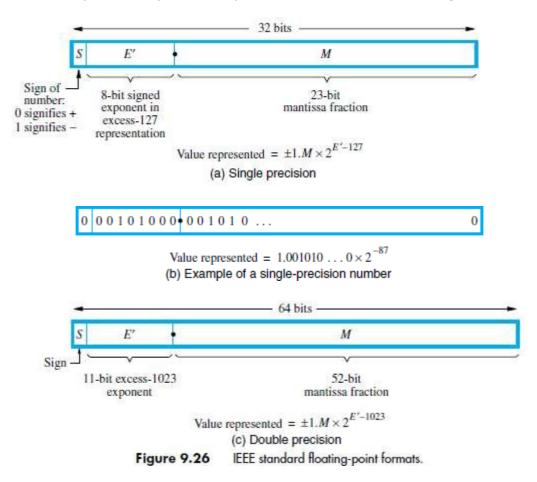

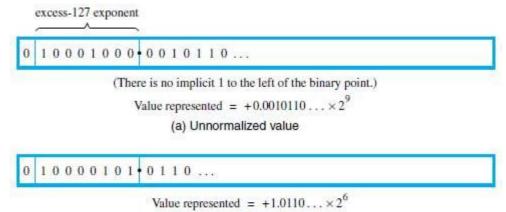

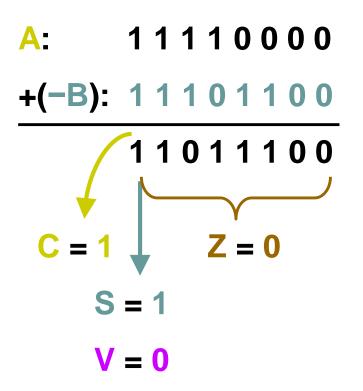

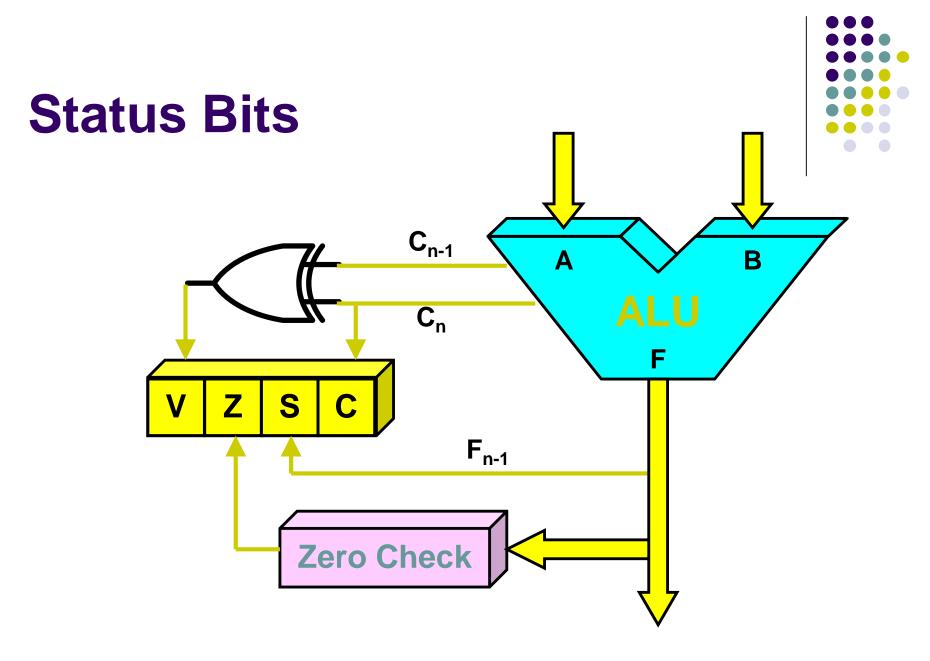

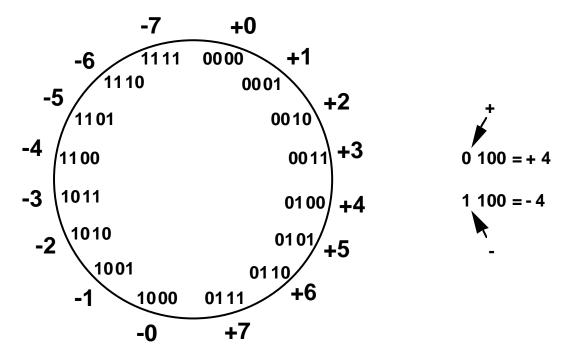

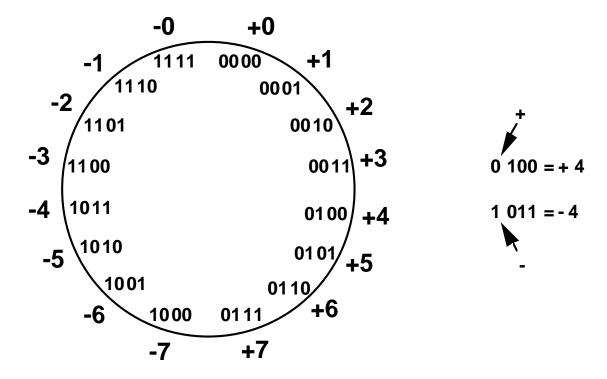

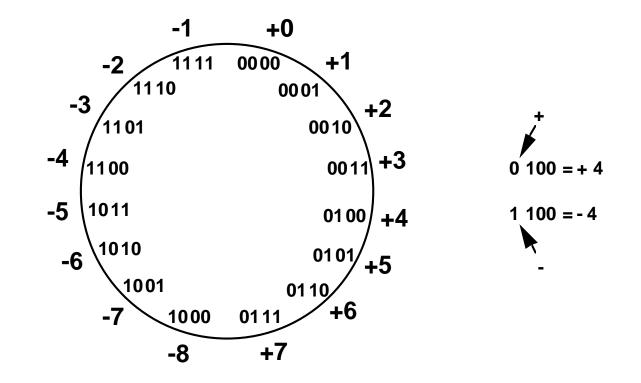

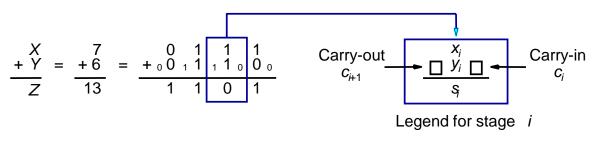

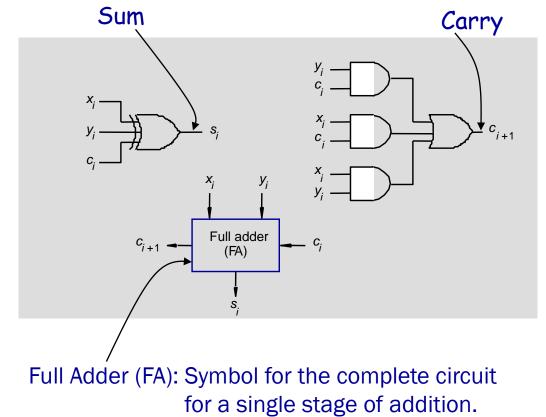

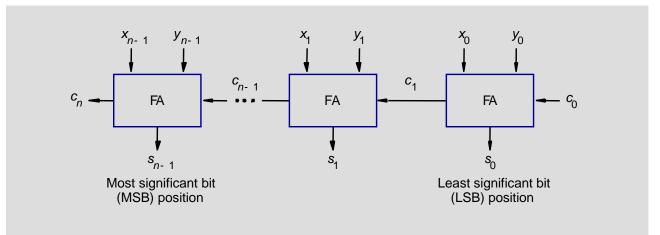

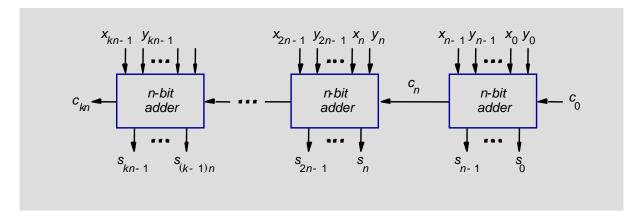

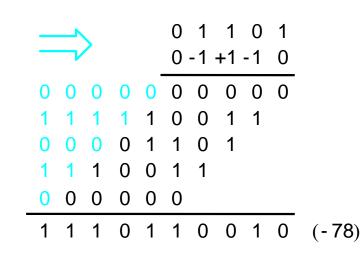

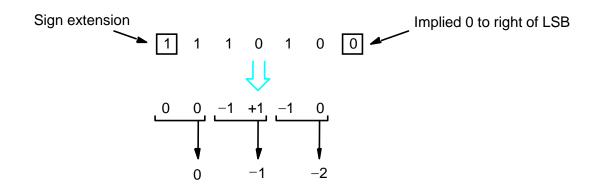

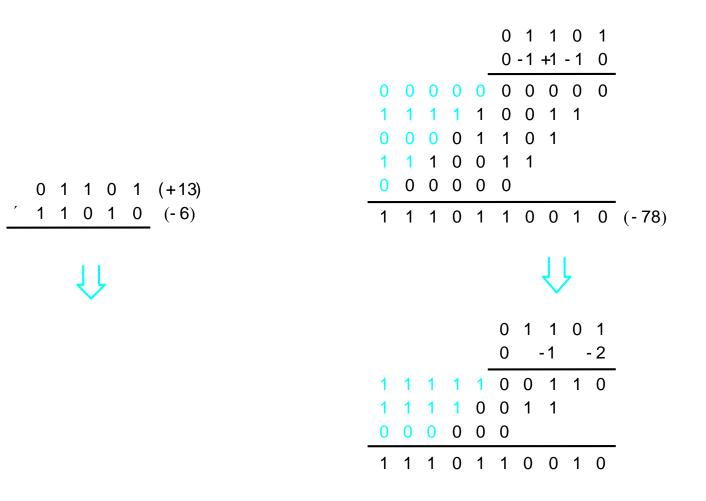

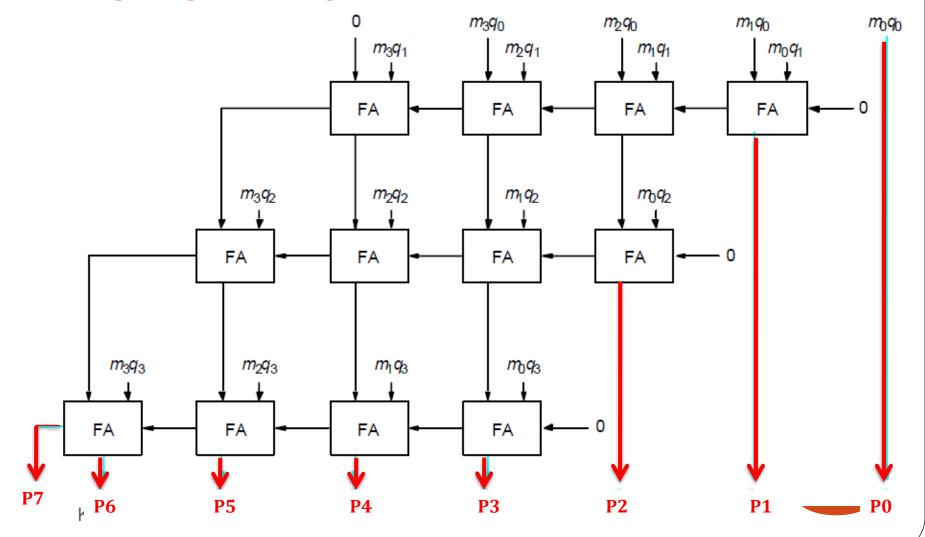

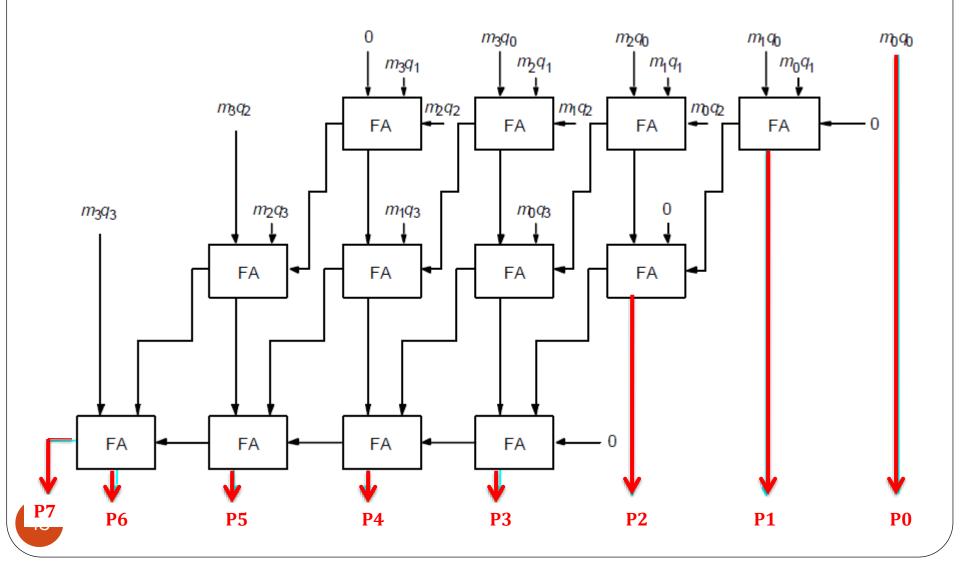

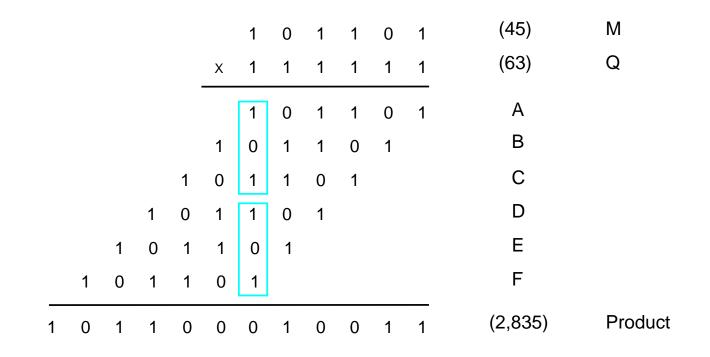

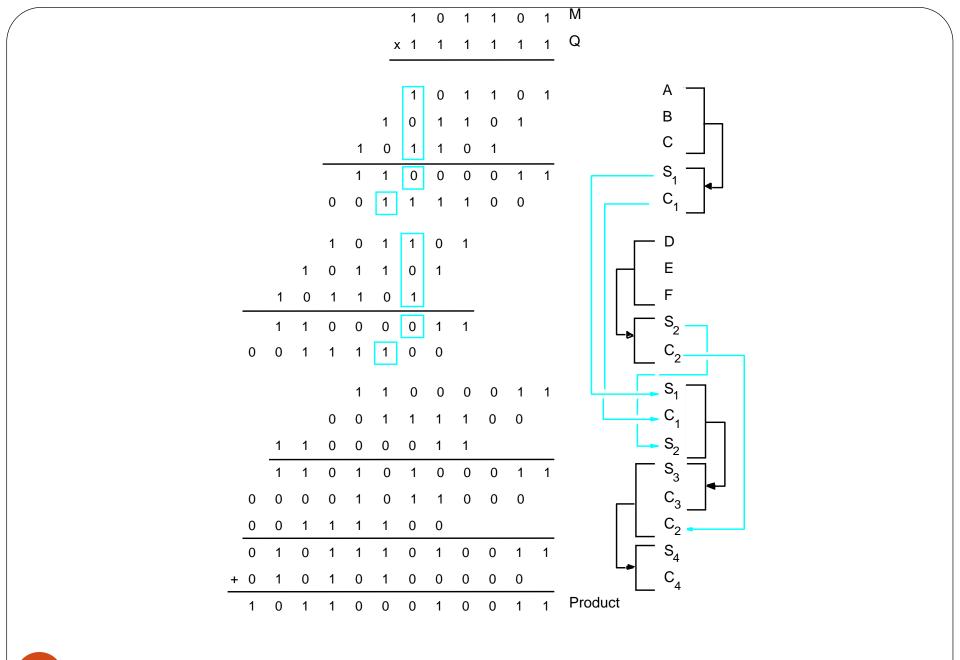

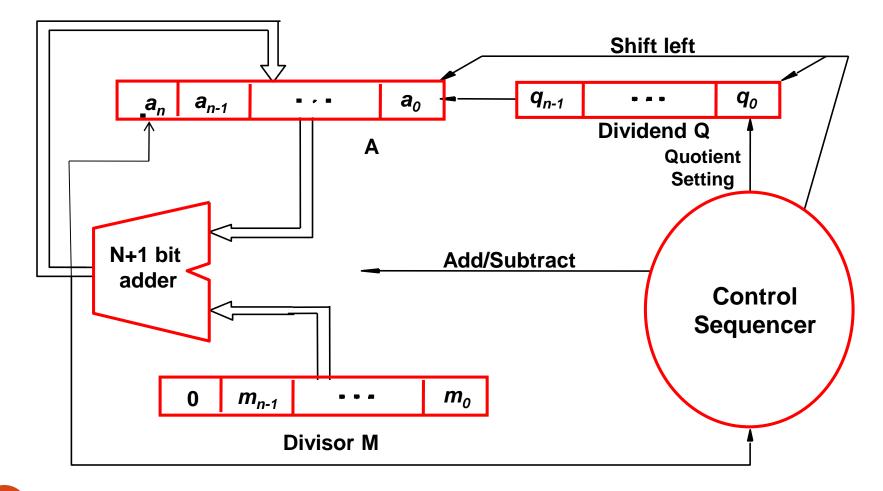

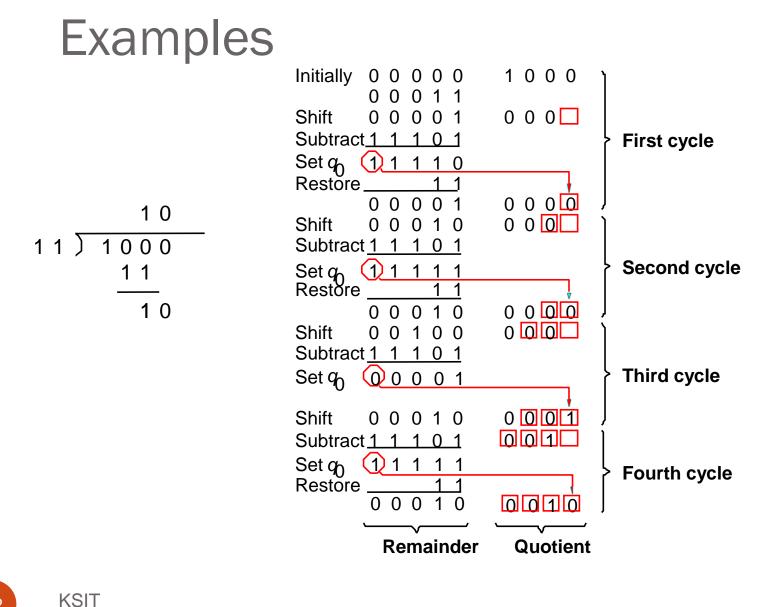

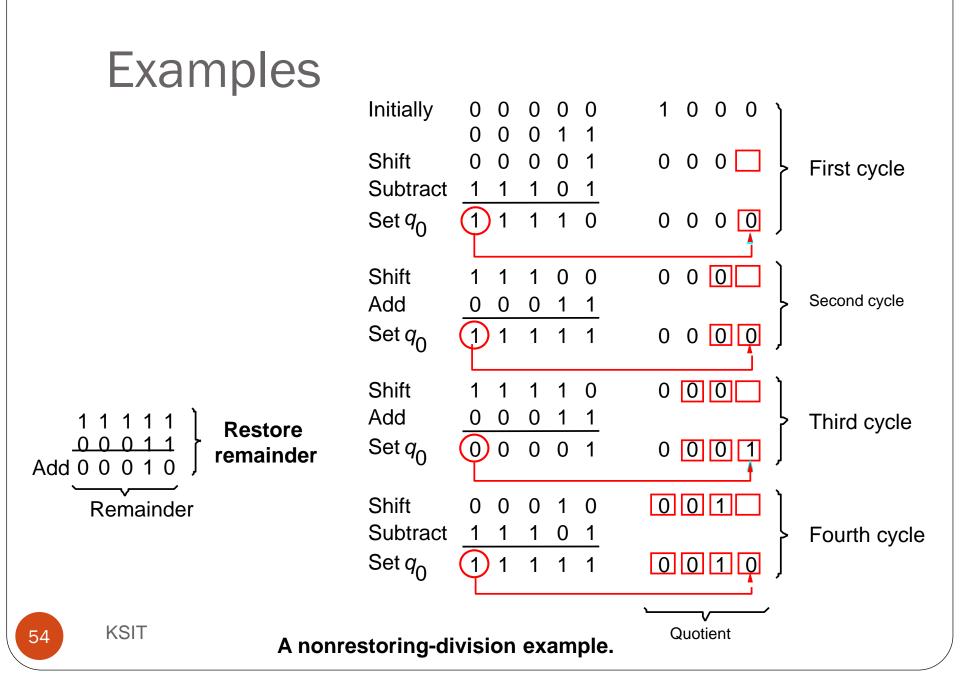

| of Signed N                                                              | Numbers, Arithmetic Operations and Characters, Addition and Subtraction<br>umbers, Design of Fast Adders, Multiplication of Positive Numbers, Signed                                                                                                                                                                                                                                                                                  | CO4<br>8 hrs                                          |  |  |  |  |

| Operand Mu                                                               | ultiplication, Fast Multiplication, Integer Division.                                                                                                                                                                                                                                                                                                                                                                                 | P01-3                                                 |  |  |  |  |

÷

| <ul><li>LO: At the end of this session the student will be able to,</li><li>1. Describe operations with integer operands</li></ul>                                                                                                                                                                                                                                                                                                                   | P02-2<br>P03-3<br>PS01-<br>PS02-                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

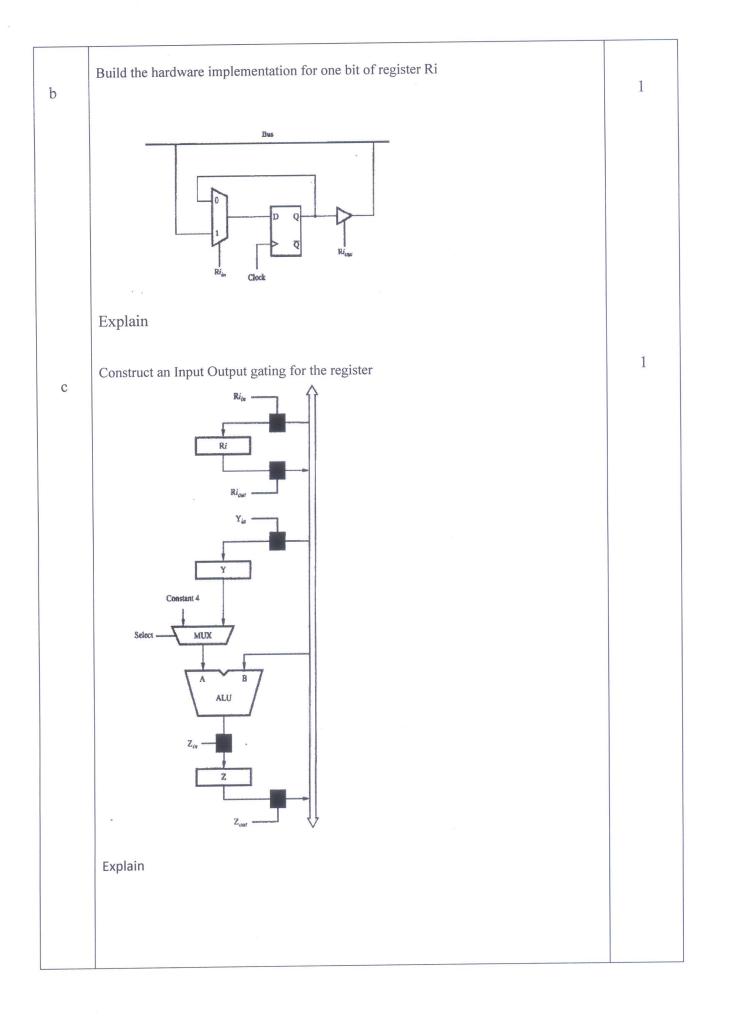

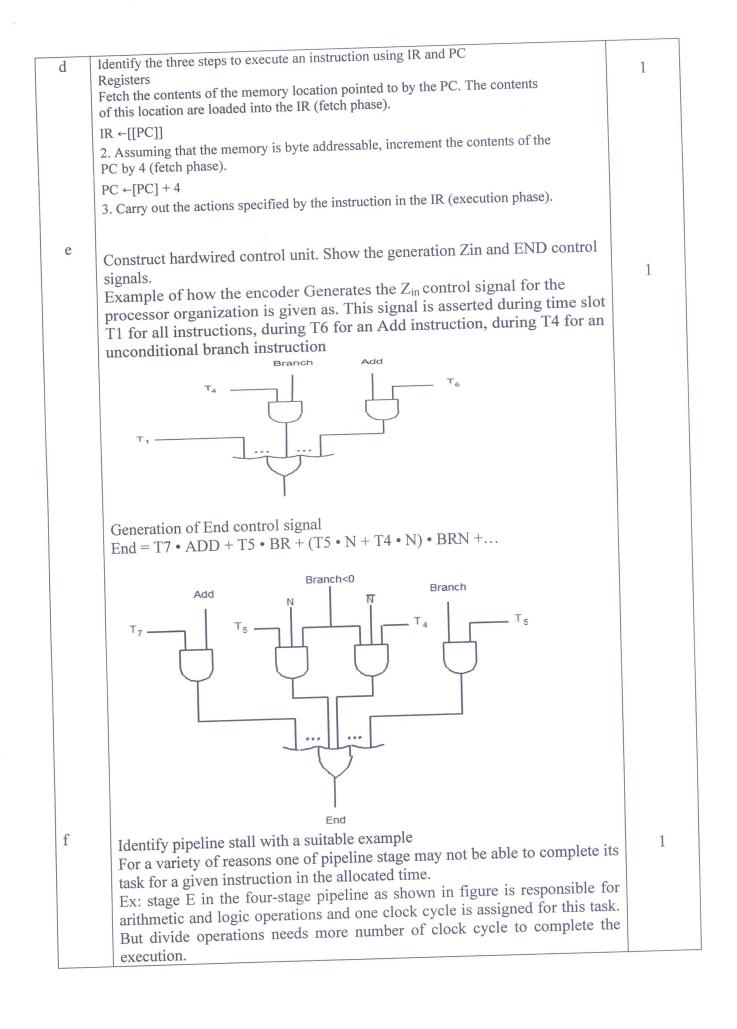

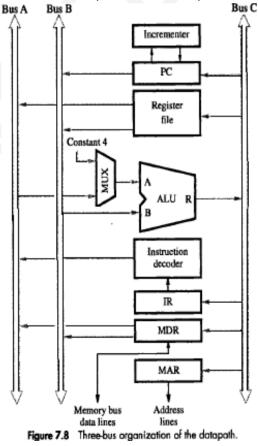

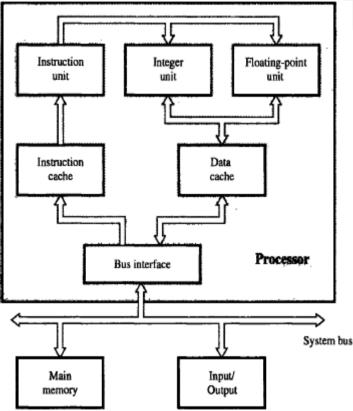

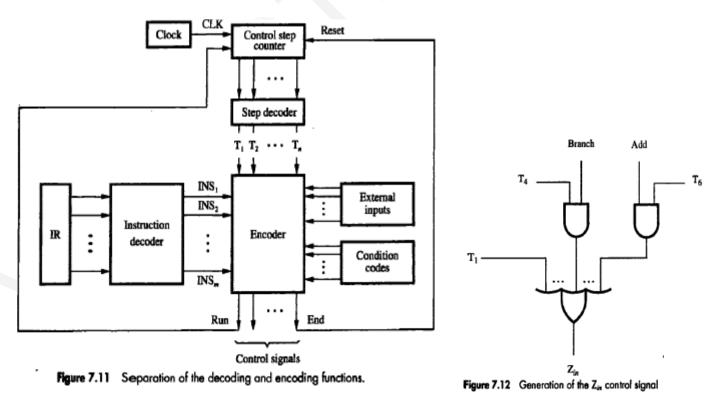

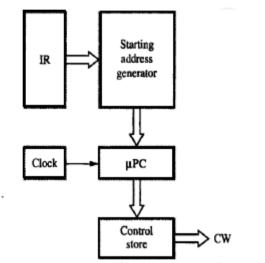

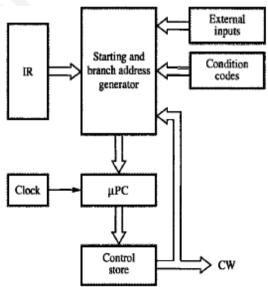

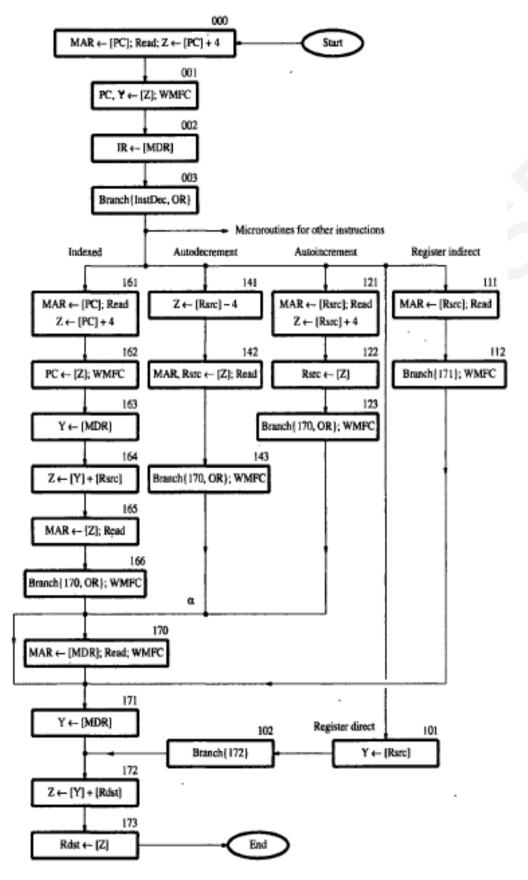

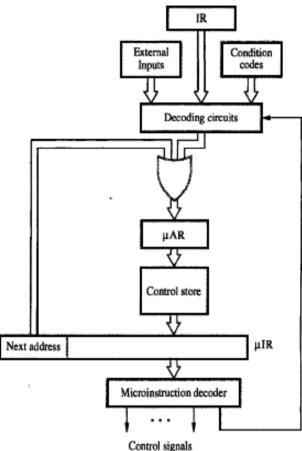

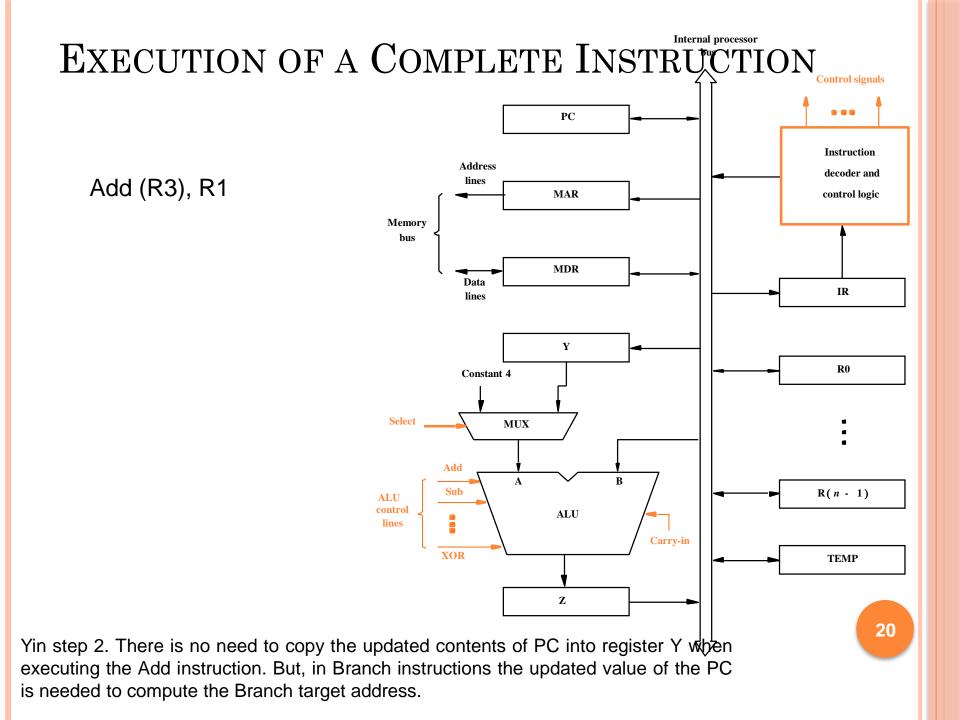

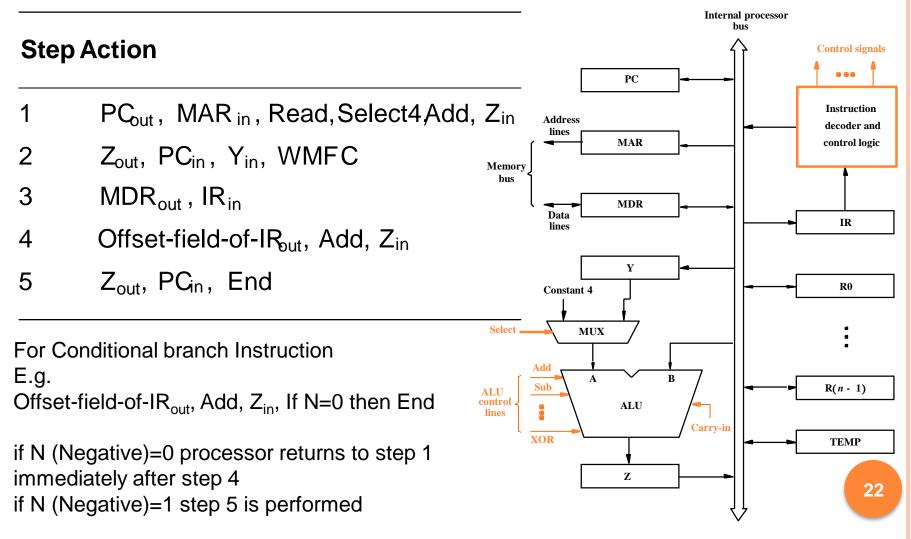

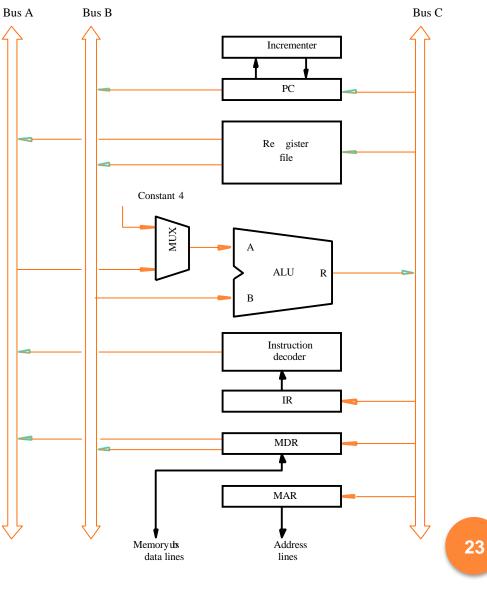

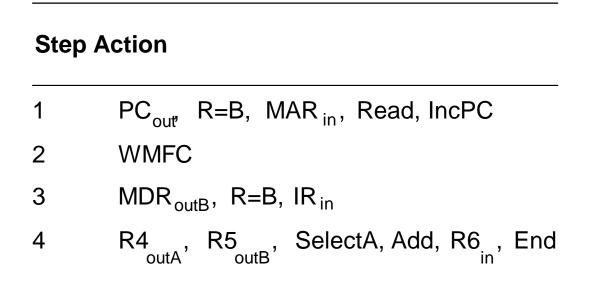

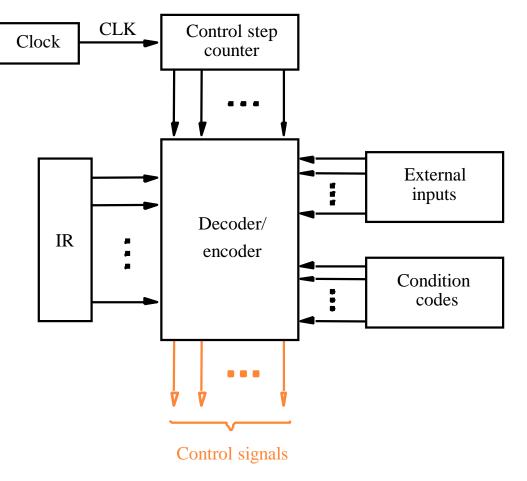

| <ul> <li>Module 5:</li> <li>Basic Processing Unit: Some Fundamental Concepts, Execution of a Complete Instruction,</li> <li>Multiple Bus Organization, Hard-wired Control, Micro programmed Control.</li> <li>Pipelining: Basic concepts of pipelining,</li> <li>LO: At the end of this session the student will be able to,</li> <li>1. Illustrate organization of a simple processor</li> <li>2. Understand basic concept of pipelining</li> </ul> | CO5<br>8 hrs<br>PO1-3<br>PO2-2<br>PO3-2<br>PSO1-<br>PSO2- |

| <b>Text Books: -</b><br>1.Carl Hamacher, Zvonko Vranesic, Safwat Zaky, Computer Organization, 5th Edition,<br>Tata McGraw Hill, 2002.                                                                                                                                                                                                                                                                                                                |                                                           |

| Reference Books:<br>1. William Stallings: Computer Organization & Architecture,9 <sup>th</sup> edition, Pearson, 2015<br>Useful Journals/ Links<br>http://nptel.vtu.ac.in/econtent/courses/CSE/06CS46/index.php                                                                                                                                                                                                                                      |                                                           |

| <ul> <li>Teaching and Learning Methods:</li> <li>1. Lecture class: 60 hrs.</li> <li>2. Self-study:</li> <li>3. Field visits/Group Discussions/Seminars:</li> </ul>                                                                                                                                                                                                                                                                                   |                                                           |

| Assessment:<br>Type of test/examination: Written examination<br>Continuous Internal Evaluation(CIE) : 40 marks (Average three of tests will be<br>considered)<br>Semester End Exam(SEE) : 60 marks (students have to answer all main questions)                                                                                                                                                                                                      |                                                           |

| Test duration: 1 :30 hr<br>Examination duration: 3 hrs                                                                                                                                                                                                                                                                                                                                                                                               |                                                           |

.

**PSO1:**Ability to understand, analyze problems and implement solutions in programming languages, as well as to apply concepts in core areas of computer Science in association with professional bodies and clubs.

**PSO2:** Ability to use computational skills and apply software knowledge to develop effective solutions and data to address real world challenges

#### **<u>CO - PO MAPPING</u>**

-

| P01: Science and engineering<br>Knowledge<br>P02: Problem Analysis<br>P03: Design & Development<br>P04:Investigations of Complex<br>Problems<br>P05: Modern Tool Usage | P07:Environment and Society<br>P08:Ethics<br>P09:Individual & Team Work<br>P010: Communication<br>P011:Project Mngmt & Finance<br>P012:Life long Learning | Pedagogy<br>quiz is<br>planned in<br>module 1<br>and 2 for<br>mapping<br>CO1 and<br>CO2 to PO9 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| PO5: Modern Tool Usage<br>PO6: Engineer & Society                                                                                                                      |                                                                                                                                                           |                                                                                                |

| СО       | Р<br>01 | PO<br>2 | P<br>O<br>3 | P<br>O<br>4 | Р<br>05 | Р<br>Об | Р<br>07 | Р<br>08 | Р<br>09 | PO<br>10 | PO<br>11 | PO<br>12 |

|----------|---------|---------|-------------|-------------|---------|---------|---------|---------|---------|----------|----------|----------|

| 18CS34.1 | 3       | 2       | 2           |             |         |         |         |         | 2       |          |          |          |

| 18CS34.2 | 3       | 2       | 2           |             |         |         |         |         | 2       |          |          |          |

| 18CS34.3 | 3       | 2       | 3           |             |         |         |         |         |         |          |          |          |

| 18CS34.4 | 3       | 2       | 3           |             |         |         |         |         |         |          |          |          |

| 18CS34.5 | 3       | 2       | 2           |             |         |         |         |         |         |          |          |          |

| 18CS34   | 3       | 2       | 2.<br>4     |             |         |         |         |         | 2       |          |          |          |

| СО       | PSO1 | PSO2 |

|----------|------|------|

| 18CS34.1 | 3    | 2    |

| 18CS34.2 | 3    | 2    |

| 18CS34.3 | 3    | 2    |

| 18CS34.4 | 3    | 2    |

| 18CS34.5 | 3    | 2    |

| 18CS34   | 3    | 2    |

| 3 | Substantial (High) Correlation |

|---|--------------------------------|

| 2 | Moderate (Medium) Correlation  |

| 1 | Slight (Low) Correlation       |

| - | No correlation.                |

deepa

dupa

Mucedrupu 6

\$

Signature of Course in-Charge

Signature of Module Coordinator

Signature of HOD

Head of the Department Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

#### K. S INSTITUTE OF TECHNOLOGY, BENGALURU-560109 TENTATIVE CALENDAR OF EVENTS: ODD SEMESTER (2020-2021) SESSION: SEP 2020 - DEC 2020

| Week | Month        |              | ·     | Da     | - X        |       | V             | Days | Activities                                                                        |

|------|--------------|--------------|-------|--------|------------|-------|---------------|------|-----------------------------------------------------------------------------------|

| No.  |              | Mon          | Tue   | Wed    | Thu        | Fri   | Sat           | Days | Activities                                                                        |

| 1    | SEP          |              | . 1 * | 2      | 3          | 4     | 5             | 5    | 1*-Commencement of Higher Semester                                                |

| 2    | SEP          | 7            | 8     | 9      | 10         | 11    | 12            | 6    |                                                                                   |

| 3    | SEP          | 14           | 15    | 16     | 17 DH      | 18    | 19            | 5    | 17- Mahalaya Amavasya                                                             |

| 4    | SEP          | 21           | 22    | 23     | 24         | 25    | 26TA          | 6    |                                                                                   |

| 5    | SEP /<br>OCT | 28 T1        | 29 T1 | 30 T1  | 1          | 2 DH  | 3             | 5    | 2- Mahatma Gandhi Jayanthi                                                        |

| 6    | ОСТ          | 5            | 6BV   | 7ASD   | 8          | 9     | 10            | 6    | 5-10 First Feed Back                                                              |

| 7    | OCT          | 12           | 13    | 14     | 15         | 16    | 17 H          | 6    |                                                                                   |

| 3    | OCT          | 19           | 20    | 21     | 22         | 23    | 24            | 6    | 24 - Monday Time Table                                                            |

| 9    | OCT          | 26 DH        | 27    | 28     | 29TA       | 30 DH | 31 DH         | 3    | 26- Vijayadashami<br>30- Eid-Milad<br>31- Maharishi Valmiki Jayanti               |

| 10   | NOV          | 2            | 3     | 4      | 5          | 6.    | 7             | 6    | 7 - Wednesday Time Table                                                          |

|      | NOV          | 9 T2         | 10 T2 | 11 T2  | 12         | 13.   | 14 H.         | 6    |                                                                                   |

| 12   | NOV          | 16 <b>DH</b> | 17 BV | 18 ASD | 19         | 20    | 21            | 5    | 16 - Balipadyami Deepavalli<br>18 - 21 Second Feed Back<br>21 - Friday Time Table |

| 13   | NOV ·        | .2,3         | 24    | 25     | 2,6        | 27    | 28 H          | 6    |                                                                                   |

| 14   | NOV<br>/DEC  | 30           | I     | 2      | 3 DH       | 4     | <b>5</b> , TA | 5    | 3- Kanakadasa Jayanti<br>5 - Monday Time Table                                    |

| 15   | DEC          | 7            | 8     | 9 LT   | 10 LT      | 11 LT | 1211          | 6    |                                                                                   |

| 16   | DEC          | 14_T3        | 15 T3 | 16 T3  | 17 *<br>BV | •     | - ,           | 4    | 17* -Last Working Day                                                             |

# Total Number of working days ( Excluding holidays and Tests)=70

| 11        | Holiday                           |

|-----------|-----------------------------------|

| BA        | Blue Book<br>Verification         |

| т1,т2, т3 | Tests 1,2, 3                      |

| ASD       | Attendance &<br>Sessional Display |

| DH        | Declared Holiday                  |

| LT        | Lab Test                          |

| ΤA        | Test attendance                   |

| Monday    | 12 |

|-----------|----|

| Tuesday   | 13 |

| Wednesday | 13 |

| Thursday  | 13 |

| Friday    | 13 |

| Saturday  | 6  |

| Total     | 70 |

K.S. INSTITUTE OF TECHNOLOGY SENGELORU 550 109

#### K. S INSTITUTE OF TECHNOLOGY, BENGALURU-560109 TENTATIVE CALENDAR OF EVENTS: ODD SEMESTER (2020-2021) SESSION: SEP 2020 - JAN 2021

|      |              |       |       |       | 04/00407 | TT CAR NO | ALC OTALL | an O an L |                                                                                   |

|------|--------------|-------|-------|-------|----------|-----------|-----------|-----------|-----------------------------------------------------------------------------------|

| Week | Month        |       | T     | Da    | Y        |           | 4         | Days      | Activities                                                                        |

| No.  |              | Mon   | Tue   | Wed   | Thu      | Fri       | Sat       | 2.4.90    |                                                                                   |

| 1    | SEP          |       | 1*    | 2     | 3        | 4         | 5         | 5         | 1*-Commencement of Higher Semester                                                |

| 2    | SEP          | 7     | 8     | 9     | 10       | 11        | 12        | 6         |                                                                                   |

| 3    | SEP          | 14    | 15    | 16    | 17 H     | 18        | 19        | 5         | 17- Mahalaya Amavasya                                                             |

| 4    | SEP          | 21    | 22    | 23    | 24       | 25        | 26TA      | 6         |                                                                                   |

| 5    | SEP /<br>OCT | 28 T1 | 29 T1 | 30 T1 | 1        | 2 H       | 3         | 5         | 2- Mahatma Gandhi Jayanthi                                                        |

| 6    | ОСТ          | 5     | 6BV   | 7ASD  | 8        | 9         | 10        | 6         | 5-10 First Feed Back                                                              |

| 7    | OCT          | 12    | 13    | 14    | 15       | 16        | 17 DH     | 5         |                                                                                   |

| 8    | ОСТ          | 19    | 20    | 21    | 22       | 23        | 24        | 6         | 24 - Monday Time Table                                                            |

| 9    | OCT          | 26 H  | 27    | 28    | 29       | 30 H      | 31 H      | 3         | 26- Vijayadashami<br>30- Eid-Milad<br>31- Maharishi Valmiki Jayanti               |

| 10   | NOV          | 2     | 3     | 4     | 5        | 6         | 7 TA      | 6         | 7 - Wednesday Time Table                                                          |

| 11   | NOV          | 9     | 10    | []    | 12 .     | 13        | 14 DH.    | 5         |                                                                                   |

| 12   | NOV          | 16 H  | 17 T2 | 18 T2 | 19 T2    | 20        | 21        | 5         | 16 - Balipadyami Deepavalli<br>18 - 21 Second Feed Back<br>21 - Friday Time Table |

| 13   | NOV          | 23    | 24BV  | 25ASD | 26       | 27        | 28 DH     | 5         |                                                                                   |

| 14   | NOV<br>/DEC  | 30    | I     | 2     | 3 H      | 4         | 5         | 5         | 3- Kanakadasa Jayanti<br>5 - Monday Time Table                                    |

| 15   | DEC          | 7     | 8     | 9     | 10       | 11        | 12 DH     | 5         |                                                                                   |

| 16   | DEC          | 14    | 15    | 16    | 17       | 18        | 19        | 6         | 19- Monday Time Table                                                             |

| 17   | DEC          | 21    | 22    | 23    | 24       | 25H       | 26DH      | 4         | 25-Christmas                                                                      |

| 18   | DEC/<br>JAN  | 28    | 29    | 30    | 31       | 1 TA      | 2         | 6         | 2Thursday Time Table                                                              |

| 19   | JAN          | 4 LT  | 5 LT  | 6 LT  | 7 LT _   | 8         | 9DH       | 5         |                                                                                   |

| 20   | JAN          | 11 T3 | 12 T3 | 13 T3 | 14H      | 15        | 16 *      | 5         | 14- Makara sankaranthi                                                            |

Total No of Working Days: 106

| н           | Holiday                           |   |

|-------------|-----------------------------------|---|

| $_{\rm BV}$ | Blue Book<br>Verification         |   |

| т1,12, т3   | Tests 1,2, 3                      | - |

| ASD         | Attendance &<br>Sessional Display |   |

| DH          | Declared Holiday                  |   |

| LT          | Lab Test                          |   |

| TA          | Test attendance                   | 1 |

|                | Monday    | 16 | 2              |

|----------------|-----------|----|----------------|

| n              | Tuesday   | 16 |                |

|                | Wednesday | 16 | L.             |

| e &<br>Display | Thursday  | 16 | K.S. INSTITUTE |

| loliday        | Friday    | 17 | BENGALU        |

| •              | Saturday  | 6  | - inconto      |

| ance           | Total     | 87 | L. L.          |

PRINCIPAL K.S. INSTITUTE OF TECHNOLOGY EENGALURU - 560 109.

16\* -Last Working Day

### K. S INSTITUTE OF TECHNOLOGY, BENGALURU-560109

DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING CALENDAR OF EVENTS: ODD SEMESTER (2020-2021) SESSION: SEP 2020 - JAN 2021

|                 | S I T        | Day   |       |       |           |         |        |      | r                                                                                                                                   | Department                                                                    |  |

|-----------------|--------------|-------|-------|-------|-----------|---------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

| Week            | Month        | Mon   | Tue   | Wed   | Thu       | Fri     | Sat    | Days | Activities                                                                                                                          | Activities                                                                    |  |

| <u>No.</u><br>1 | SEP          | MOII  | 1*    | 2     | 3         | 4       | 5      | 5    | 1*-Commencement of<br>Higher Semester                                                                                               |                                                                               |  |

| 2               | SEP          | 7     | 8     | 9     | 10        | 11      | 12     | 6    |                                                                                                                                     | *****                                                                         |  |

| 3               | SEP          | 14    | 15    | 16    | 1711      | 18      | 19     | 5    | 17- Mahalaya                                                                                                                        |                                                                               |  |

| 4               | SEP          | 21    | 22    | 23    | 24        | 25      | 26TA   | 6    |                                                                                                                                     |                                                                               |  |

| 5               | SEP /<br>OCT | 28 T1 | 29 T1 | 30 T1 | 1         | 2.11    | 3      | 5    | 2- Mahatma Gandhi<br>Jayanthi                                                                                                       |                                                                               |  |

| 6               | ОСТ          | 5     | 6BV   | 7ASD  | 8         | 9       | 10     | 6    | 5-10 First Feed Back                                                                                                                |                                                                               |  |

| 7               | ОСТ          | 12    | 13    | 14    | 15        | 16      | 17 DH  | 5    |                                                                                                                                     |                                                                               |  |

| 8               | ост          | 19    | 20    | 21    | 22        | 23      | 24     | 6    | 24 - Monday Time<br>Table                                                                                                           |                                                                               |  |

| 9               | ОСТ          | 26 H  | 27    | 28    | 29        | 30 11   | 31 11  | 3    | 26- Vijayadashami<br>30- Eid-Milad<br>31- Maharishi Valmiki<br>Jayanti                                                              | Project Zeroth Review<br>Presentation                                         |  |

| 10              | NOV          | 2     | 3     | 4     | 5         | 6       | 7 TA   | 6    | 7 - Wednesday Time<br>Table                                                                                                         |                                                                               |  |

| 11              | NOV          | 9     | 10    | 11    | 12        | 13      | 14 DH  | 5    |                                                                                                                                     | 13-11-2020 Webinar<br>An Insight into Web<br>Application<br>Development       |  |

| 12              | NOV          | 16 H  | 17 T2 | 18 T2 | 19 T2     | 20      | 21     | 5    | <ul> <li>16 - Balipadyami</li> <li>Deepavalli</li> <li>18 - 21 Second Feed</li> <li>Back</li> <li>21 - Friday Time Table</li> </ul> |                                                                               |  |

| 13              | NOV          | 23    | 24BV  | 25ASD | 26        | 27      | 28 DH  | 5    |                                                                                                                                     |                                                                               |  |

| 14              | NOV<br>/DEC  | 30    | 1     | 2     | 38        | 4       | 5      | 5    | 3- Kanakadasa Jayanti<br>5 - Monday Time<br>Table                                                                                   | Project Zeroth Phase<br>Re-Presentation                                       |  |

| 15              | DEC          | 7     | 8     | 9     | 10        | 11      | 12 DH  | 5    |                                                                                                                                     |                                                                               |  |

| 16              | DEC          | 14    | 15    | 16    | 17        | 18      | 19     | 6    | 19- Monday Time                                                                                                                     |                                                                               |  |

| 17              | DEC          | 21    | 22    | 23    | 24        | 258     | 26DH   | 4    | 25-Christmas                                                                                                                        | 22-12-2020 & 23-12-<br>2020 34th CSI<br>Karnataka State<br>Student Convention |  |

| 18              | DEC/<br>JAN  | 28    | 29    | 30    | 31        | 1 TA    | 2      | 6    | 2Thursday Time Table                                                                                                                | Project Phase - 1<br>Review Presentation                                      |  |

| 19              | JAN          | 4 LT  | 5 LT  | 6LT   | 7 LT      | 8       | 9DII   | 5    | 14- Makara                                                                                                                          |                                                                               |  |

| 20              | JAN          | 11 T3 | 12 T3 | 13 T3 | 14H       | 15      | 16 *   | 5    | 14- Makara<br>sankaranthi                                                                                                           |                                                                               |  |

|                 |              |       |       | Tota  | I No of V | Vorking | Days : | 106  |                                                                                                                                     |                                                                               |  |

Total Number of working days (Excluding holidays and Tests)=87

|              | otal Number of   |

|--------------|------------------|

| II           | Holiday          |

| BV           | Blue Book        |

| T1,T2,<br>T3 | Tests 1,2, 3     |

| ASD          | Attendance &     |

| DH           | Declared Holiday |

| LT           | Lab Test         |

| TA           | Test attendance  |

|              |                  |

| avs (Excluding h | ondays a |

|------------------|----------|

| Monday           | 16       |

| Tuesday          | 16       |

| Wednesday        | 16       |

| Thursday         | 16       |

| Friday           | 17       |

| Saturday         | 6        |

| Total            | 87       |

Head of the Department Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

#### K. .S. INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING III SEM A SECTION STUDENT DETAILS:2020-21

| SI. No | USN        | Student Name              | Email ID                                               | Mobile Number |  |  |

|--------|------------|---------------------------|--------------------------------------------------------|---------------|--|--|

| 1      | 1KS19CS001 | AAKRITI                   | aaki96798nov@gmail.com                                 | 8102100946    |  |  |

| 2      |            | ABHISHEK B                | abhibgowda2001@gmail.com                               | 8296520760    |  |  |

| 3      |            | ABHISHEK YADAV            | abhishekyaadav1998@gmail.com                           | 6394788936    |  |  |

| 4      |            | ADITH KARTHIK RAJU        | adithkarthik10@gmail.com                               | 9164875273    |  |  |

| 5      |            | AJAY S KALBURGI           | kalburgiajay@gmail.com                                 | 7090663930    |  |  |

| 6      | 1KS19CS006 | AKASH A S                 | akashlisp@gmail.com                                    | 8088125905    |  |  |

| 7      | 1KS19CS007 | AMAN KUSHWAHA             | amankushwaha365@gmail.com                              | 8081239899    |  |  |

| 8      | 1KS19CS008 | AMILINENI HARINI          | amilinenivenkatrshulu924@gmail.com                     | 8919756866    |  |  |

| 9      | 1KS19CS008 | AMILINEIN HARIN           | baluamit@gmail.com                                     | 9483354792    |  |  |

|        |            | AMOGHA H S                | amogha.hs@gmail.com                                    | 9845006222    |  |  |

| 10     | 1KS19CS010 | AMRUTHA K H               | amruthaharshan8347@gmail.com                           | 7204219550    |  |  |

| 11 12  | 1KS19CS012 | ANAGHA A HEBBAR           | anaghaah01@gmail.com                                   | 9148571180    |  |  |

|        | 1KS19CS012 |                           | vbabuvbabu222@gmail.com                                | 9342582372    |  |  |

| 13     |            |                           | aqsa.aqeel17@gmail.com                                 | 8707566256    |  |  |

| 14     |            | AQSA AQEEL                | ashikananjegowda869@gmail.com                          | 7975007345    |  |  |

| 15     |            | ASHIKA H N                | mohan_iist@yahoo.co.in                                 | 9980150041    |  |  |

| 16     |            | BHOOMIKA A M              | bhoomikak17@gmail.com                                  | 9986598304    |  |  |

| 17     | 1KS19CS018 | BHOOMIKA K                | ravikumar19721736@gmail.com                            | 9964151736    |  |  |

| 18     |            | BHUMIKA M                 |                                                        | 6366306846    |  |  |

| 19     | 1KS19CS020 |                           | sheryascn611@gmail.com<br>chaitanyashivaraju@gmail.com | 8197730165    |  |  |

| 20     | 1KS19CS021 | CHAITANYA SHIVARAJU       | chaitanyashivaraju@gmail.com                           |               |  |  |

| 21     | 1KS19CS022 | CHANDAN B V               | chandanbv9123@gmail.com                                | 7338568147    |  |  |

| 22     | 1KS19CS023 | DEEKSHA NAIDU R           | deeksha12082001@gmail.com                              | 8095122655    |  |  |

| 23     | 1KS19CS024 |                           | deepa1012gandhi@gmail.com                              | 9148483322    |  |  |

| 24     |            | DEEPTHI.N.K               | deepthink400@gmail.com                                 | 9148487058    |  |  |

| 25     |            | DEVI PRASAD N             | deviprasad4556@gmail.com                               | 7639444564    |  |  |

| 26     | 1KS19CS028 | DHEEMANTH G               | dheemanthgirish03@gmail.com                            | 9108250916    |  |  |

| 27     | 1KS19CS029 | DINESH M                  | denishdinu1431@gmail.coom                              | 6366055811    |  |  |

| 28     | 1KS19CS030 | G PRERITHA                | prerithagowtham@gmail.com                              | 8197458531    |  |  |

| 29     | 1KS19CS031 | GAGAN REDDY S             | gagan19200@gmail.com                                   | 8277884917    |  |  |

| 30     | 1KS19CS032 | GAGANDEEP K               | gagandeepk6549@gmail.com                               | 7619129339    |  |  |

| 31     |            | GEETHANJALI B K PRASAD    | geethanjali9840@gmail.com                              | 9632806412    |  |  |

| 32     |            | GULSHAN KUMAR S           | kumargulshan2702@gmail.com                             | 8050991314    |  |  |

| 33     |            | HARSHITHA J               | harshithaj2306@gmail.com                               | 6360781608    |  |  |

| 34     |            | INDRAJITH H M             | indrajithlikith@gmail.com                              | 9972503057    |  |  |

| 35     |            | JEEVAN T O                | jjeevanto1227@gmail.com                                | 9353380159    |  |  |

| 36     | 1KS19CS037 |                           | kishanuk2002@gmail.com                                 | 9686480814    |  |  |

| 37     |            | K R VAGEESH               | vageesh2001@gmail.com                                  | 9742578725    |  |  |

|        | 1KS19CS039 | KALYAN CHOWDHARY B        | munirathnam931@gmail.com                               | 9008838499    |  |  |

| 38     | 1KS19CS040 | KARTHIK S MORAJKAR        | karthik.morajkar26@gmail.com                           | 9113629181    |  |  |

| 39     |            | KAVYASHREE.S.L            | kavyashreesl599@gmail.com                              | 9113274206    |  |  |

| 40     | 1KS19CS042 | KEERTHAN GOWDA S          | keerthangowdas222@gmail.com                            | 9845871477    |  |  |

| 41     | 1KS19CS043 |                           | sreeja16112002@gmail.com                               | 9491465760    |  |  |

| 42     | 1KS19CS044 | KOTHAPALLI SREEJA         | steejator12002@gman.com                                |               |  |  |

| 43     | 1KS19CS045 | KOTTALA SAIVENKATASUCHITH | suchithkottala@gmail.com                               | 9059089926    |  |  |

| 44     |            | KRISHNA K R               | krkrishna2626@gmail.com                                | 7358478255    |  |  |

| 45     | 1KS19CS040 |                           | chittihoney225@gmail.com                               | 9591084850    |  |  |

| 45     | 1KS19CS047 |                           | likhithgk01@gmail.com                                  | 9448116636    |  |  |

| 40     | 1KS19CS048 |                           | lishachoudhary2612@gmail.com                           | 9036831198    |  |  |

| 47     |            | MAHAK SHREE               | shreemahak01@gmail.com                                 | 9973580148    |  |  |

| 48     | 1KS19CS050 | MALLIPALLI SPURTHI REDDY  | mspurthi49@gmail.com                                   | 9440090436    |  |  |

|        |            | MALLIPALLI SPORTHI REDDT  | manasagl@gmail.com                                     | 9901599887    |  |  |

| 50     | 1KS19CS052 | IVIANASA U L              | manasagiugman.com                                      |               |  |  |

| 51     |            | MOHAMMED NOOR AMAN        | mohammednooraman569@gmail.com                          | 9880672867    |  |  |

| 52     | 1KS19CS054 | MUKESH KUMAR              | mukeshkeshri114@gmail.com                              | 7991448599    |  |  |

| 53     |            | MYTHREYI U                | shobha.hande8@gmail.com                                | 9741052966    |  |  |

| 54     | 1KS19CS056 |                           | ashoknashok132000@gmail.com                            | 8073952496    |  |  |

| 55     | 1KS19CS057 |                           | bhavyanarra56@gmail.com                                | 8790762175    |  |  |

| 56     | 1KS19CS058 |                           | shashanknp02@gmail.com                                 | 9606573173    |  |  |

| 57     | 1KS18CS011 | BHARATH R                 | barathrahul100@gmail.com                               | 7795844959    |  |  |

| 58     | 1KS20CS400 |                           | -                                                      | 9845038115    |  |  |

HOD-CSE

Head of the Department Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

### K.S. INSTITUTE OF TECHNOLOGY, BENGALURU-109 DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING

III SEMESTER ONLINE CLASS TIME TABLE FOR THE YEAR 2020-21 (ODD SEMESTER)(TENTATIVE)

W.E.F: 01-09-2020

CLASS TEACHER:Mr. Sanjoy Das

SEC: 'A'

| PERIOD      | 1                     | 2                     | 12.00 434             | 3                     | 4                     |                       | 5                                                  | 6                     |  |

|-------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------------------------------------|-----------------------|--|

| TIME<br>DAY | 09:00 AM-<br>10:00 AM | 10:00 AM-<br>11.00 AM | 11:00 AM-<br>11.15 AM | 11:15 AM-<br>12:15 PM | 12:15 PM-<br>01.15 PM | 01:15 PM-<br>01:45 PM | 01:45PM-<br>02:45 PM                               | 02:45 PM- 03:45<br>PM |  |

| MON         | со                    | ADE                   |                       | TCFS & NT             | DMS                   |                       | C DS LAB                                           |                       |  |

| TUE         | DMS                   | SE                    |                       | TCFS & NT             | DSA                   | BREAK                 | < ADE LAB                                          |                       |  |

| WED         | TCFS & NT             | ADE                   | BREAK                 | DSA                   | SE                    |                       | KANNADA                                            |                       |  |

| THUR        | SE                    | DMS                   | BR                    | CO                    | ADE                   | LUNCH                 | PLACEMENT ACTIVITIES                               |                       |  |

| FRI         | со                    | TCFS & NT             |                       | DMS                   | DSA                   | E                     | TUTORIAL/PEDAGOGY ADDITION<br>ACTIVITIES MATHEMATI |                       |  |

| SAT         | ADE                   | co                    |                       | SE                    | DSA                   |                       | TUTORIAL/PEDAGOGY KANNAD<br>ACTIVITIES (Non Kannad |                       |  |

| Subject Code    | Subject Name                                                                                          | Faculty Name                                          |

|-----------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 18MAT31         | TRANSFORM CALCULUS, FOURIER SERIES AND<br>NUMERICAL TECHNIQUES                                        | Mr. Chowdappa M R                                     |

| 18CS32          | DATA STRUCTURES AND APPLICATIONS                                                                      | Mrs. Vijayalaxmi M                                    |

| 18CS33          | ANALOG AND DIGITAL ELECTRONICS                                                                        | Mr. Sanjoy Das                                        |

| 18CS34          | COMPUTER ORGANIZATION                                                                                 | Mrs. Deepa S R                                        |

| 18CS35          | SOFTWARE ENGINEERING                                                                                  | Dr. Dayananda R B                                     |

| 18CS36          | DISCRETE MATHEMATICAL STRUCTURES                                                                      | Mr. Kushal Kumar B N                                  |

| 18CSL37         | ANALOG AND DIGITAL ELECTRONICS LABORATORY                                                             | Mr. Sanjoy Das & Mrs. Deepa S R                       |

| 18CSL38         | DATA STRUCTURES LABORATORY                                                                            | Mrs. Vijayalaxmi M & Mrs. Ranjitha K N & Mrs. Beena K |

| 18KVK39/18KAK39 | VYAVAHARIKA KANNADA (KANNADA FOR<br>COMMUNICATION)/<br>AADALITHA KANNADA (KANNADA FOR ADMINISTRATION) | Mr. Thrimurthy                                        |

graft L\_\_\_\_ (L == 1 TIME TABLE INCHARGE

mucutap

HOD Head of the Department Dept of Computer Science & Engg

|                                                                                                                                                                                                                                                                                                  | MPUTER ORGAN<br>from the academic                                                             |                                                                                                        |                       |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-------------|

| Enterne                                                                                                                                                                                                                                                                                          | SEMESTER -                                                                                    | III                                                                                                    |                       |             |

| Course Code                                                                                                                                                                                                                                                                                      | 18CS34                                                                                        | CIE Marks                                                                                              | 40                    |             |

| Number of Contact Hours/Week                                                                                                                                                                                                                                                                     | 3:0:0                                                                                         | SEE Marks                                                                                              | 60                    |             |

| Total Number of Contact Hours                                                                                                                                                                                                                                                                    | 40                                                                                            | Exam Hours                                                                                             | 03                    |             |

|                                                                                                                                                                                                                                                                                                  | CREDITS -                                                                                     | 3                                                                                                      |                       |             |

| Course Learning Objectives: This course                                                                                                                                                                                                                                                          | urse (18CS34) will e                                                                          | enable students to:                                                                                    |                       |             |

| • Explain the basic sub systems of                                                                                                                                                                                                                                                               | of a computer, their                                                                          | organization, structure and                                                                            | operation             | 1.          |

| • Illustrate the concept of program                                                                                                                                                                                                                                                              | ms as sequences of 1                                                                          | machine instructions.                                                                                  |                       |             |

| • Demonstrate different ways of                                                                                                                                                                                                                                                                  | communicating with                                                                            | h I/O devices and standard                                                                             | I/O interf            | aces.       |

| <ul> <li>Describe memory hierarchy and</li> </ul>                                                                                                                                                                                                                                                | d concept of virtual                                                                          | memory.                                                                                                |                       |             |

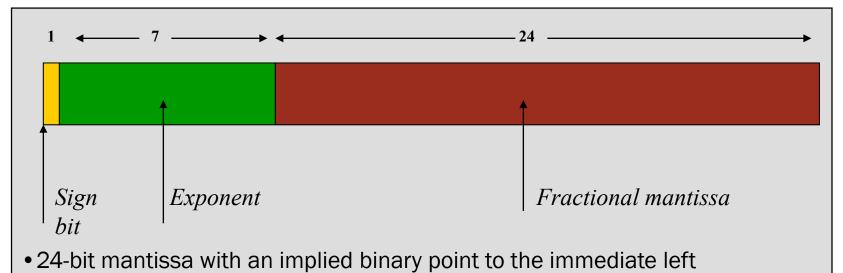

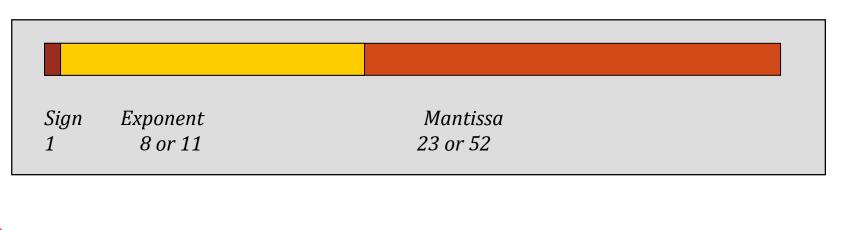

| <ul> <li>Describe arithmetic and logical</li> </ul>                                                                                                                                                                                                                                              | operations with inte                                                                          | eger and floating-point ope                                                                            | rands.                |             |

| <ul> <li>Illustrate organization of a simple</li> </ul>                                                                                                                                                                                                                                          | ple processor, pipeli                                                                         | ned processor and other co                                                                             | mputing               | systems.    |

| Module 1                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                        |                       | Contac      |

|                                                                                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                       | Hours<br>08 |

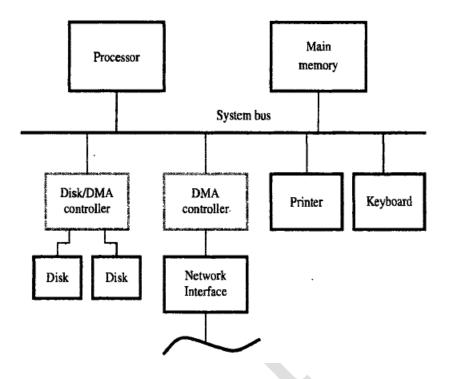

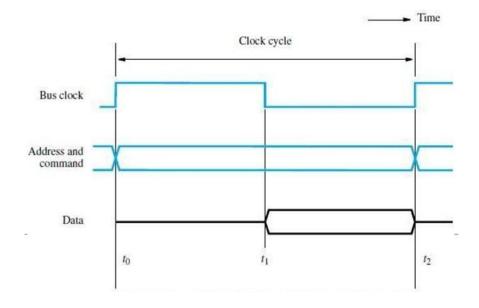

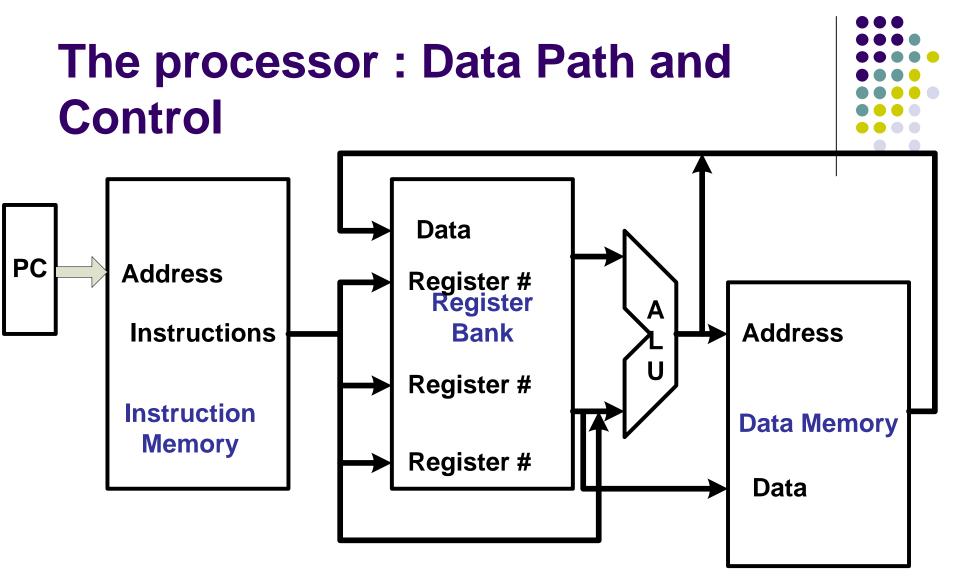

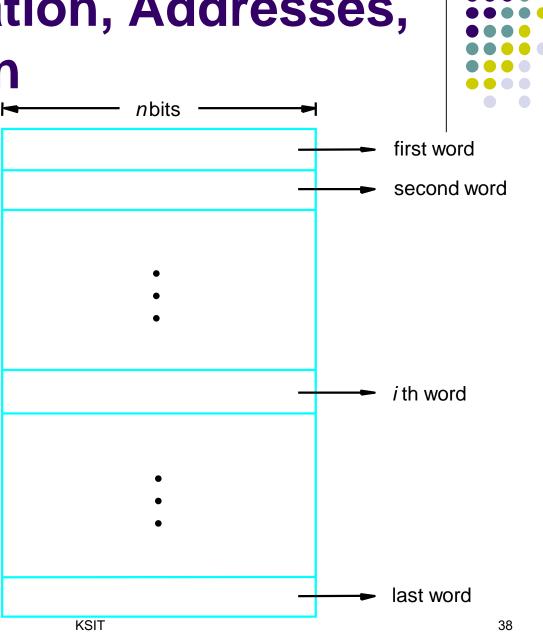

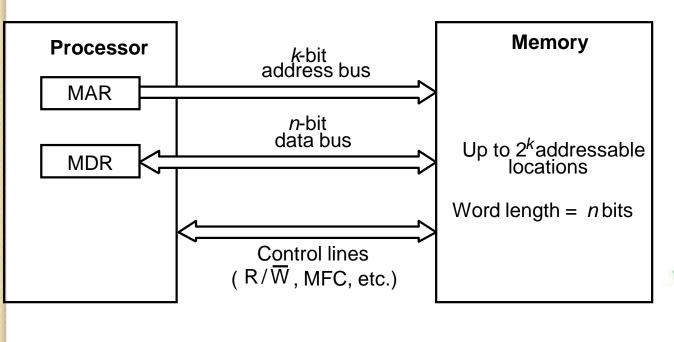

| Basic Structure of Computers: Basic<br>Processor Clock, Basic Performance<br>Machine Instructions and Progra<br>Operations, Instructions and Instru<br>Language, Basic Input and Output Op<br>Instructions, Encoding of Machine Inst<br>Text book 1: Chapter1 – 1.3, 1.4, 1.6<br>RBT: L1, L2, L3 | Equation, Clock<br>ams: Memory Lou<br>action Sequencing,<br>perations, Stacks and<br>ructions | Rate, Performance Measu<br>cation and Addresses, I<br>Addressing Modes, A<br>d Queues, Subroutines, Ad | Memory<br>ssembly     |             |

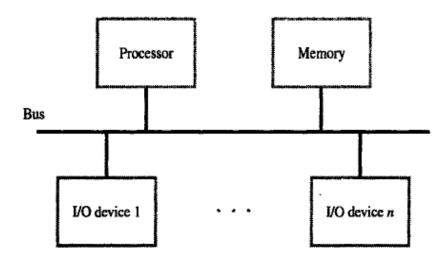

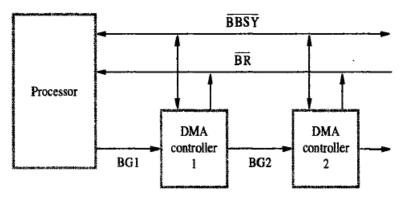

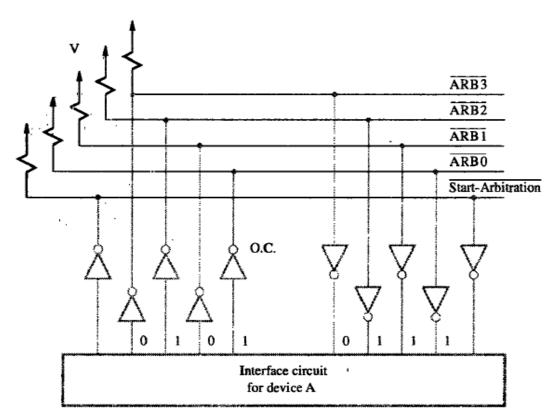

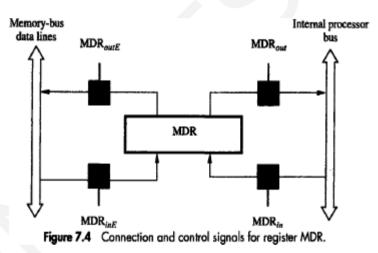

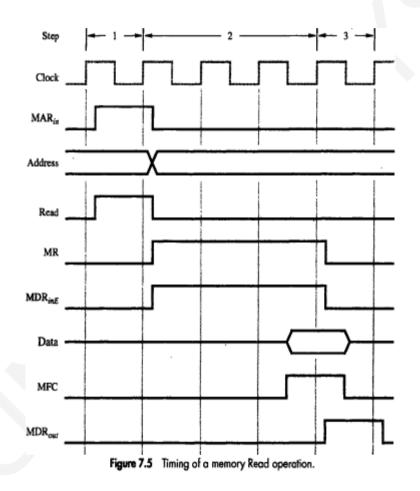

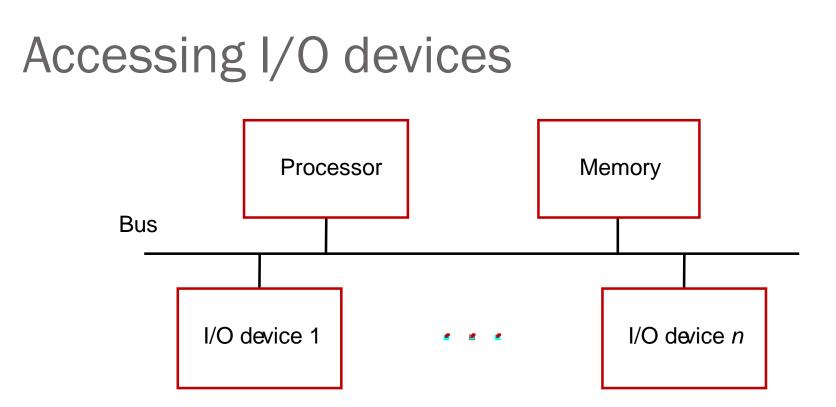

| Module 2                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                        | Di                    | 00          |

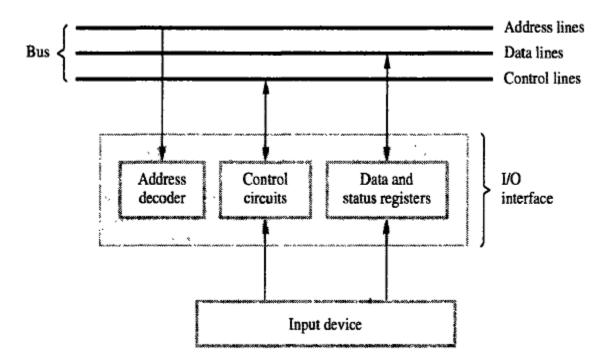

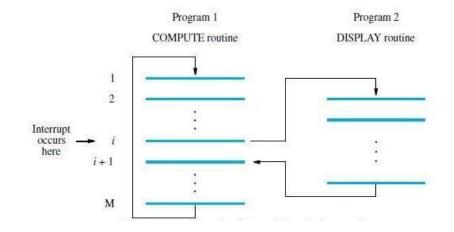

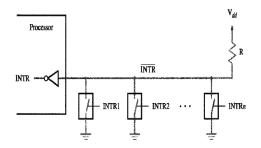

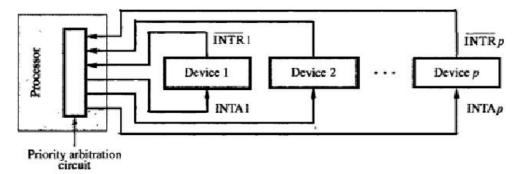

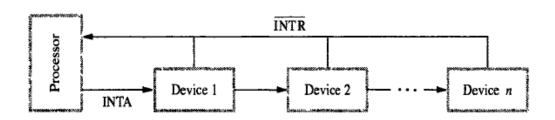

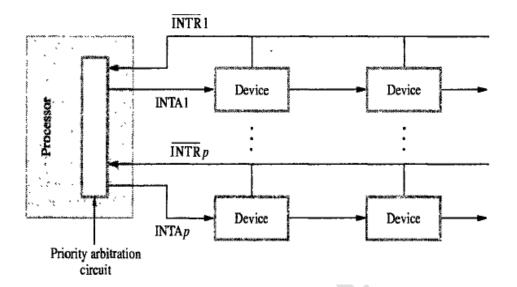

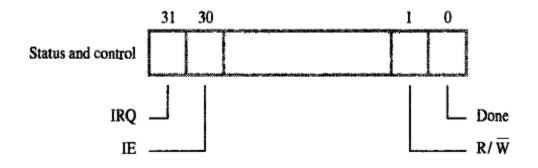

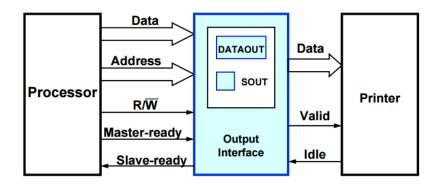

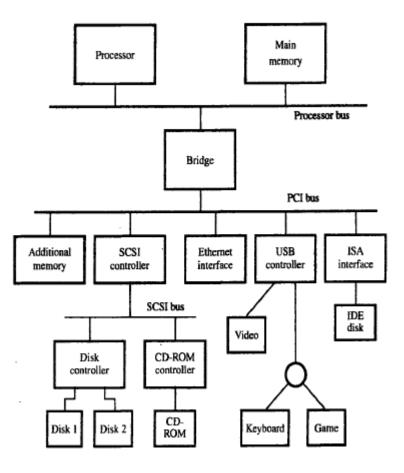

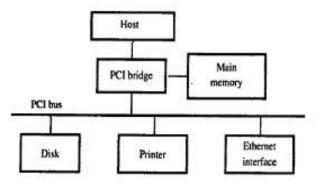

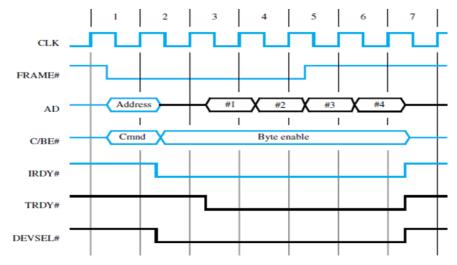

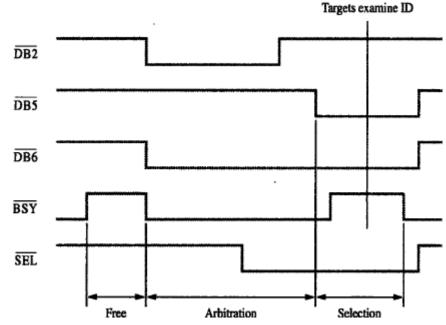

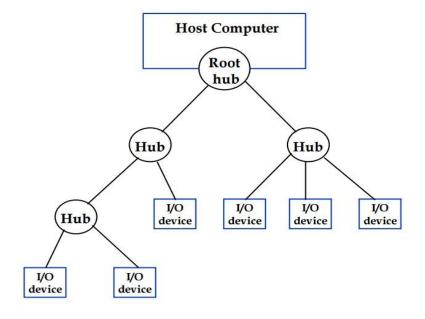

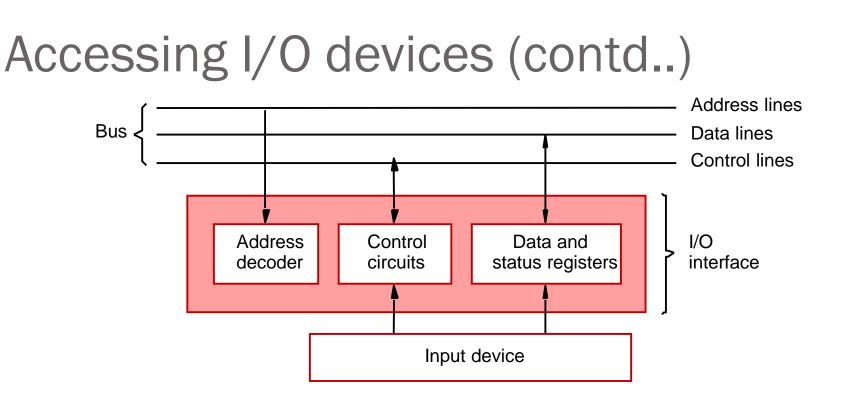

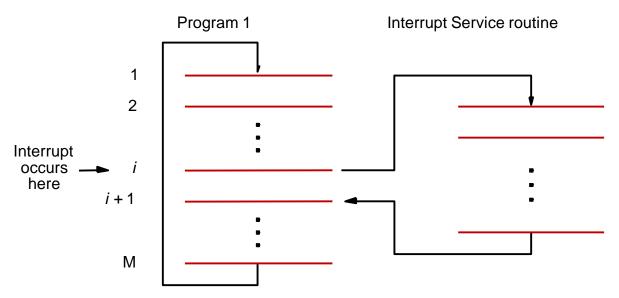

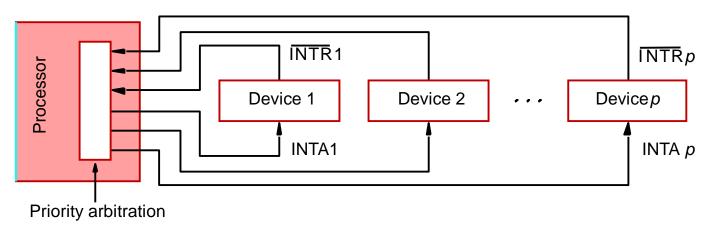

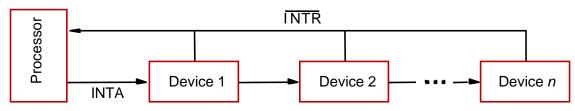

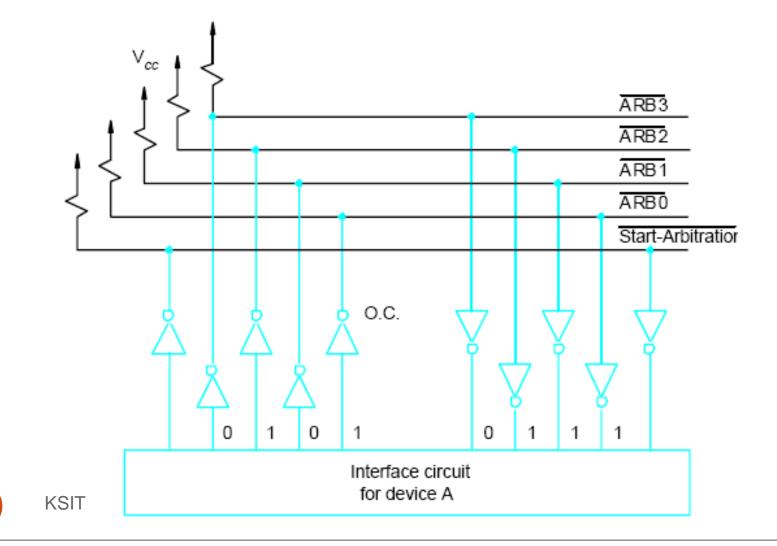

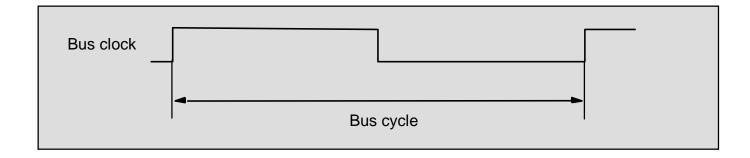

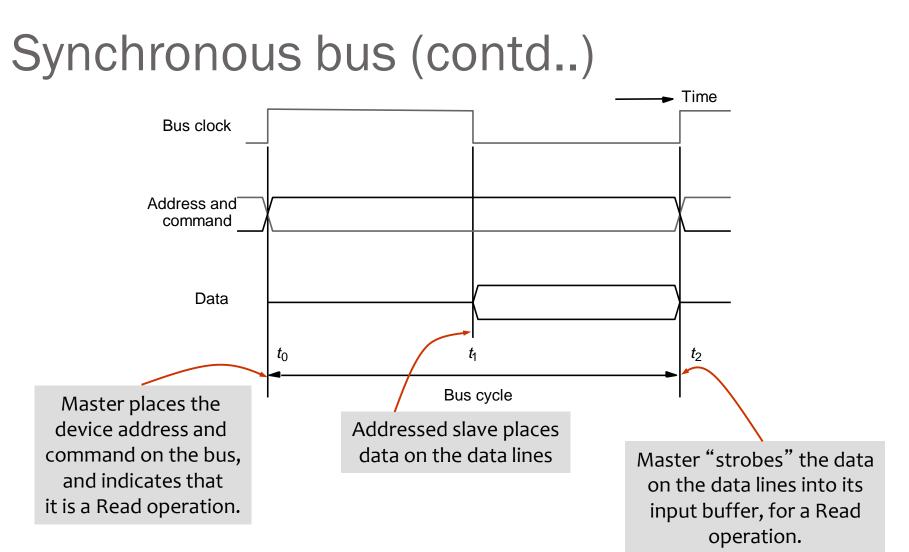

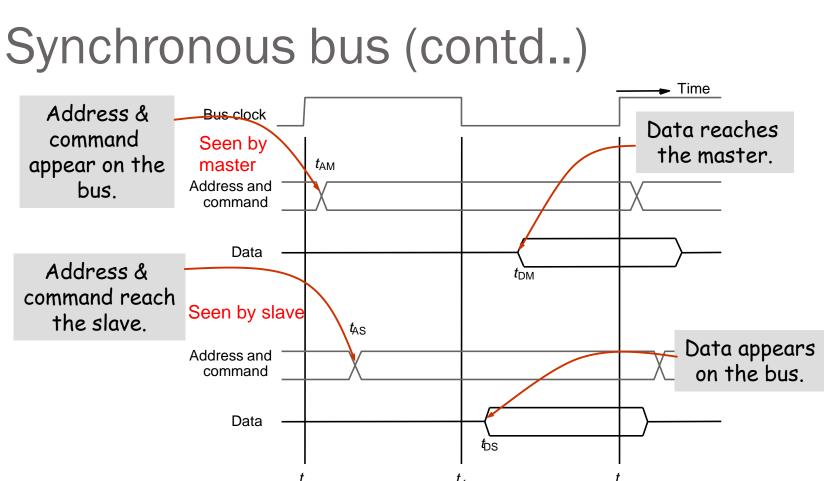

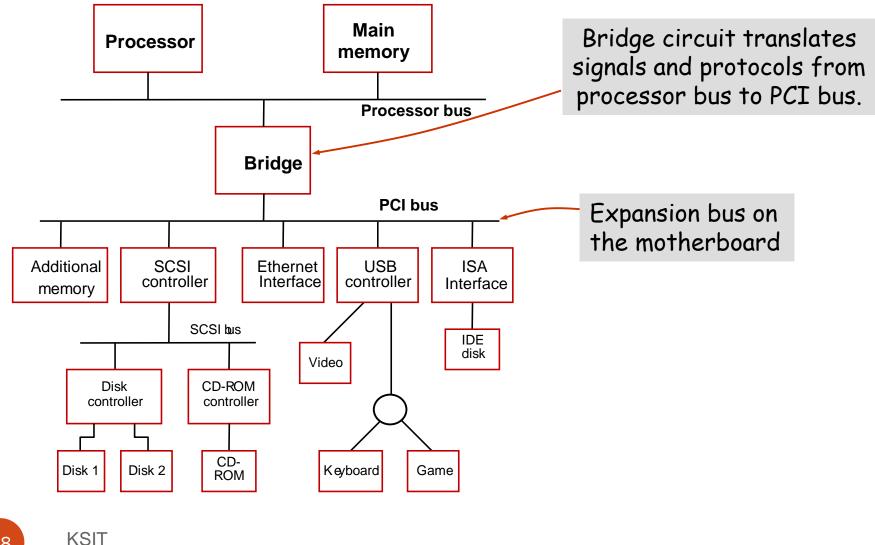

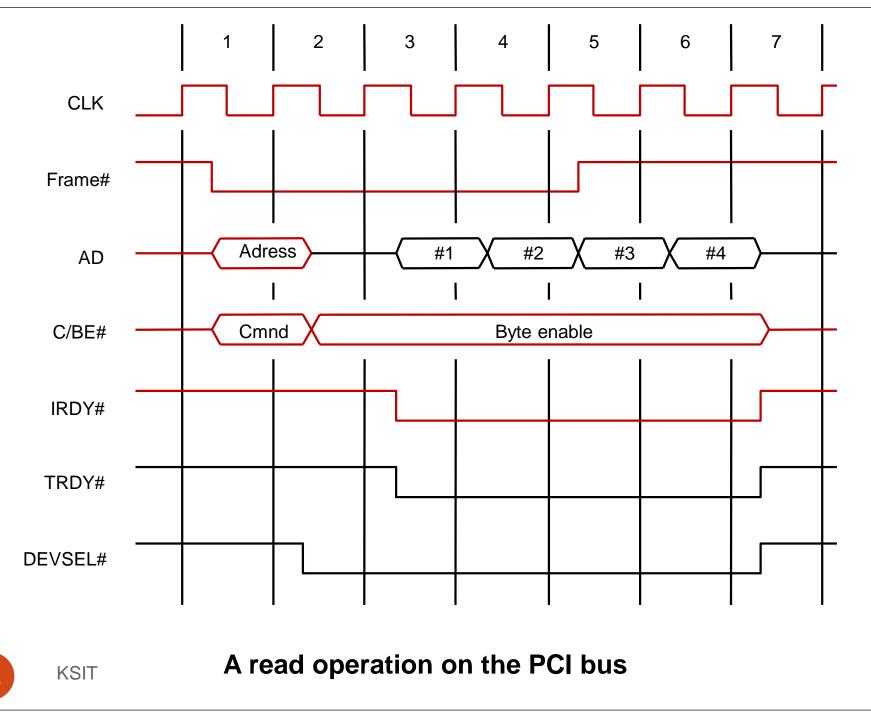

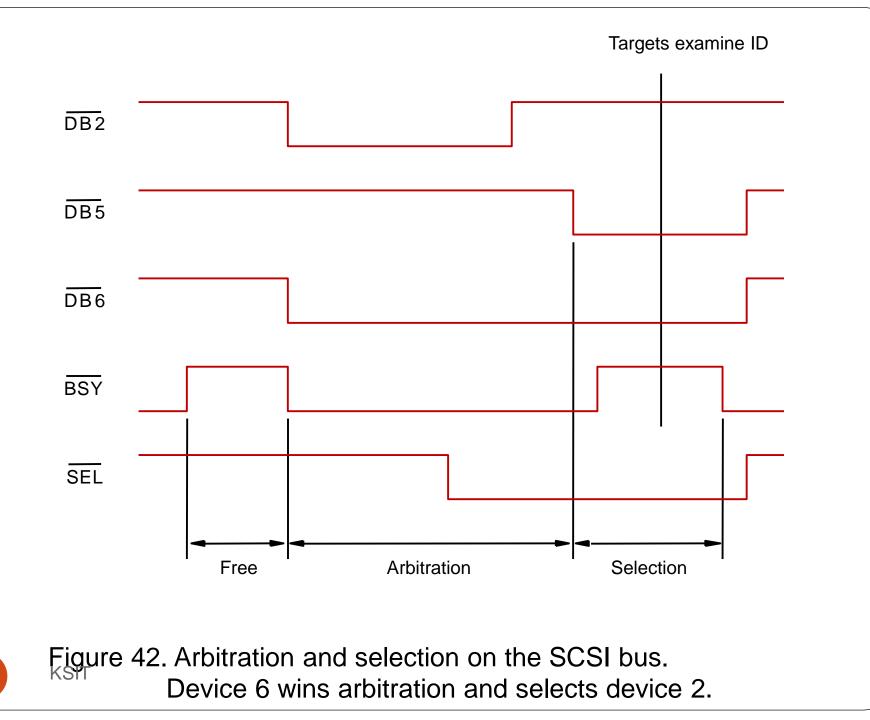

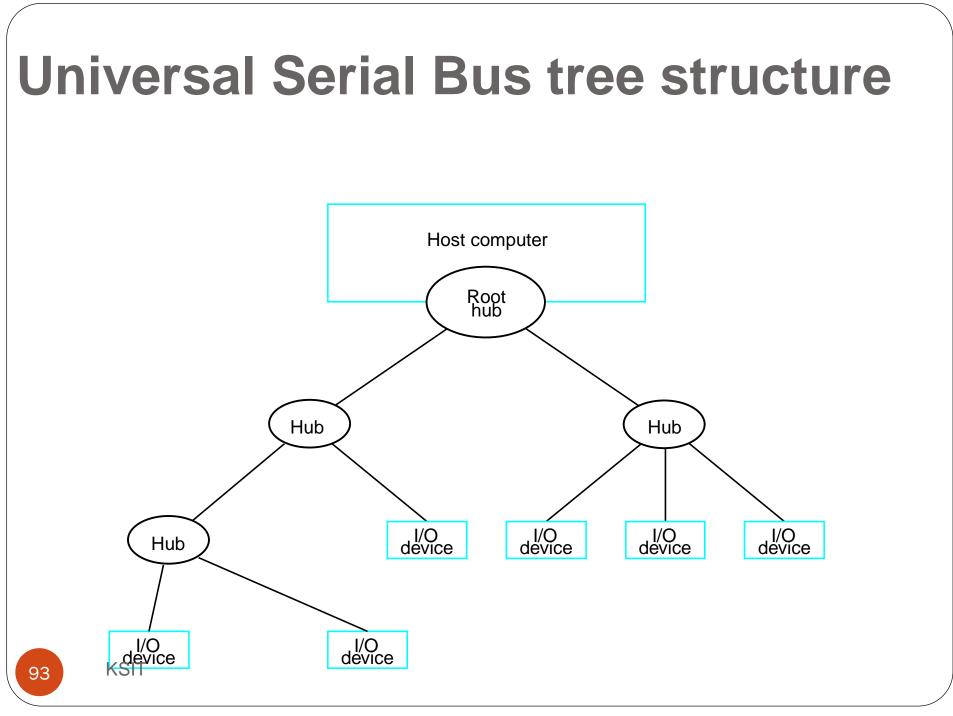

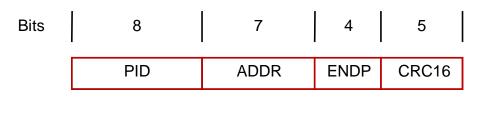

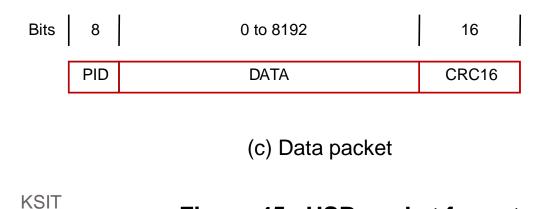

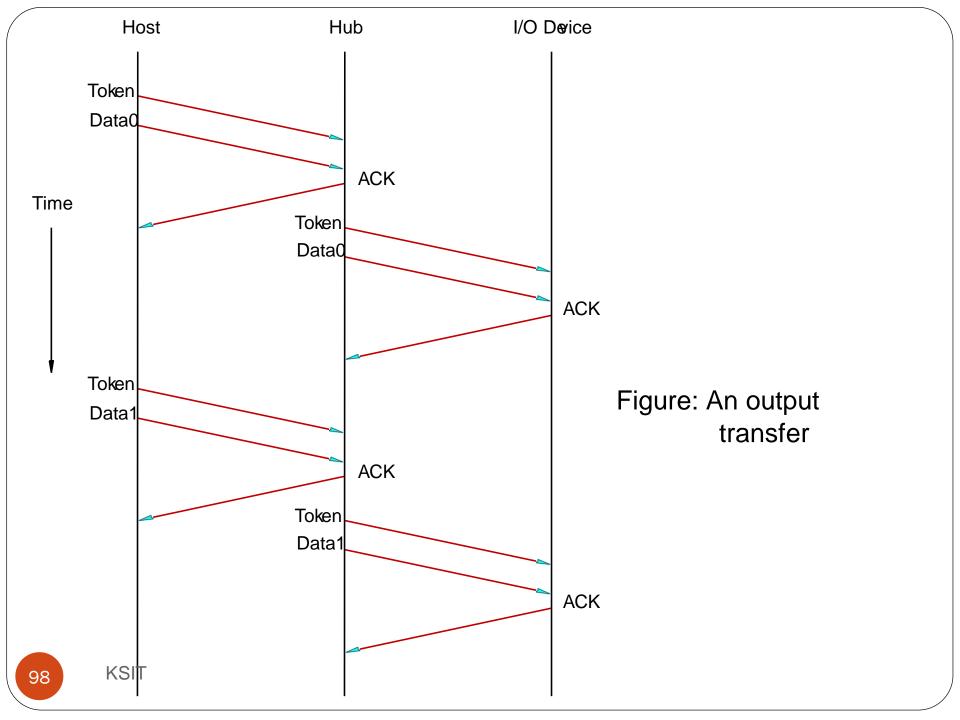

| Input/Output Organization: Accessin<br>Memory Access, Buses, Interface Cir<br>USB.<br>Text book 1: Chapter4 – 4.1, 4.2, 4.4<br>RBT: L1, L2, L3                                                                                                                                                   | cuits, Standard I/O                                                                           | Interfaces – PCI Bus, SC                                                                               | CSI Bus,              | 08          |

| Module 3                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                        |                       | 0.0         |

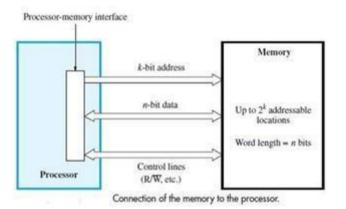

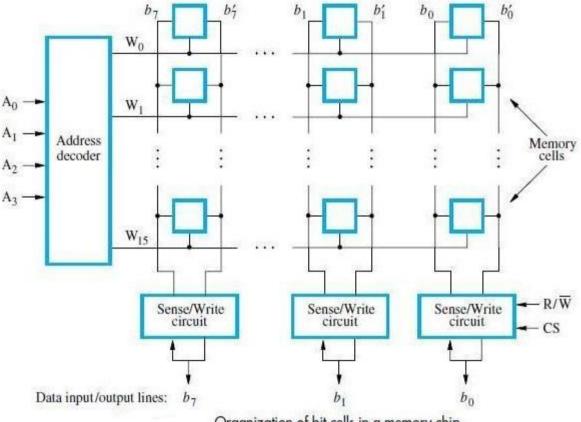

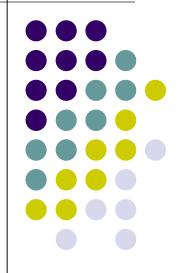

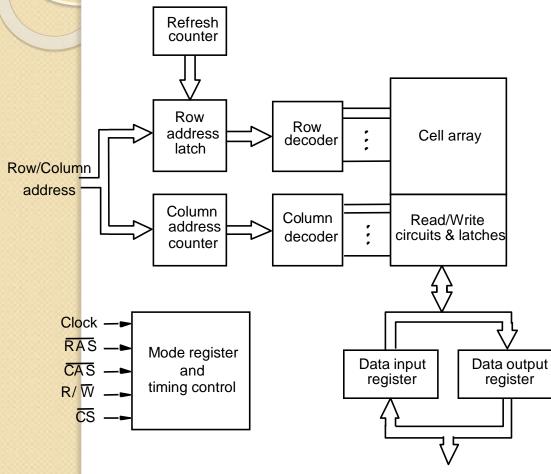

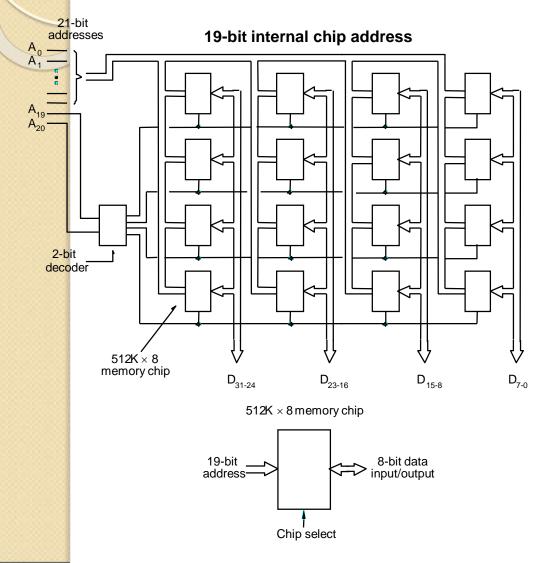

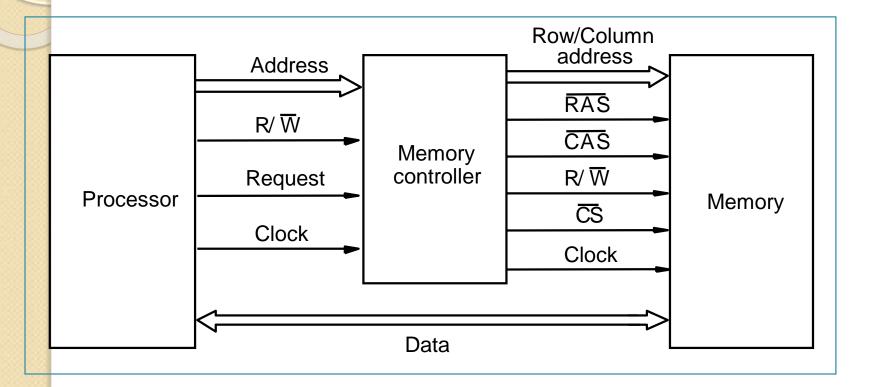

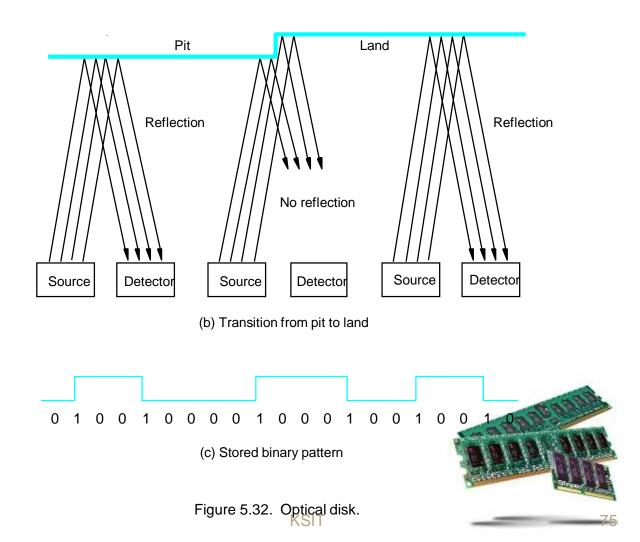

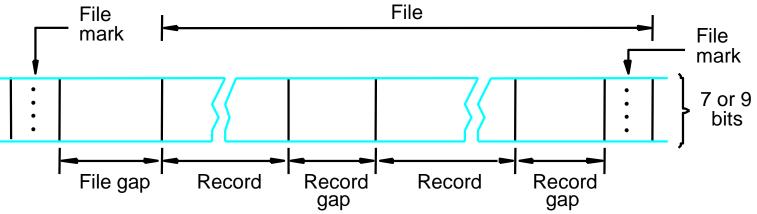

| Memory System: Basic Concepts, Se<br>Speed, Size, and Cost, Cache Memo<br>Performance Considerations.<br>Text book 1: Chapter5 – 5.1 to 5.4, 5<br>RBT: L1, L2, L3                                                                                                                                | ories – Mapping Fu                                                                            | inctions, Replacement Alg                                                                              | emories,<br>;orithms, | 08          |

| Modulo 4                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                        |                       |             |

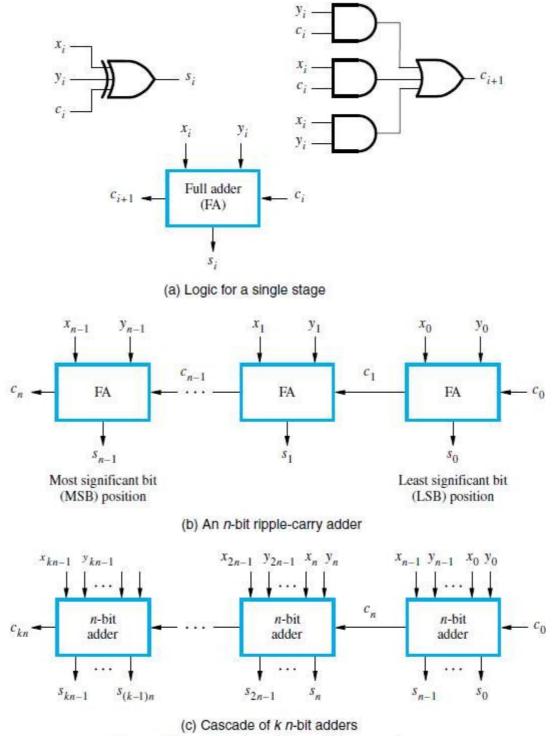

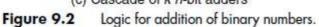

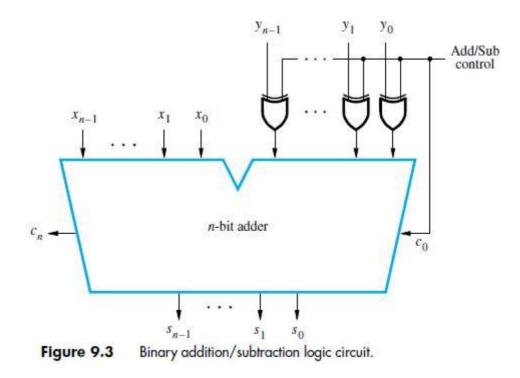

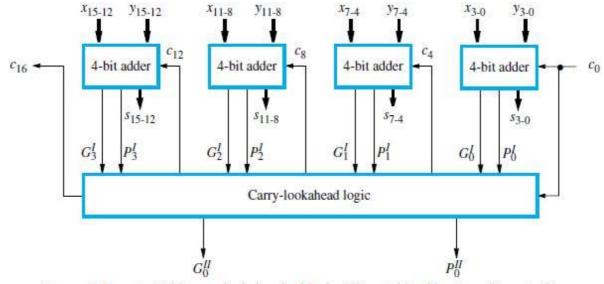

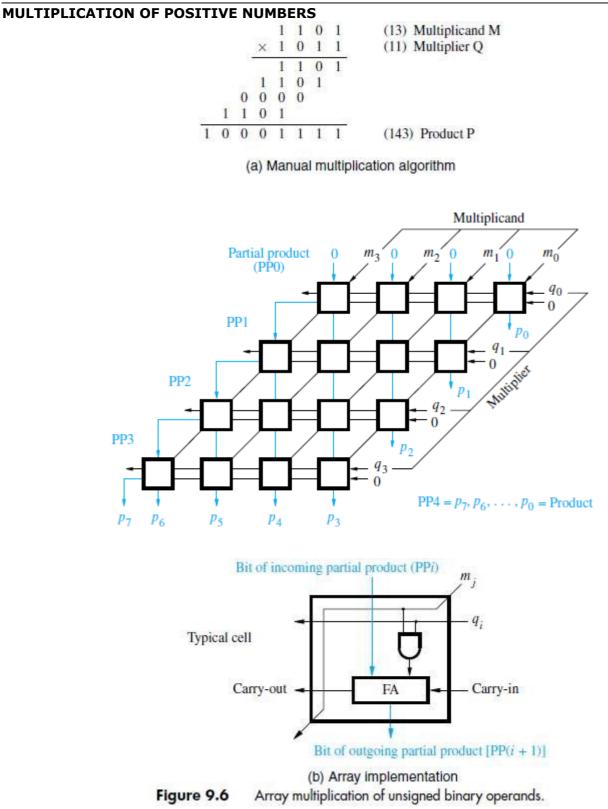

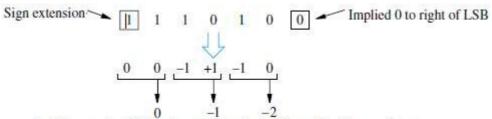

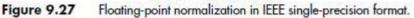

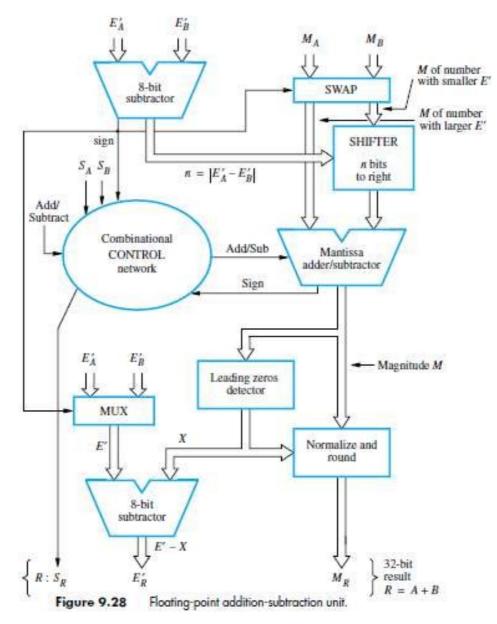

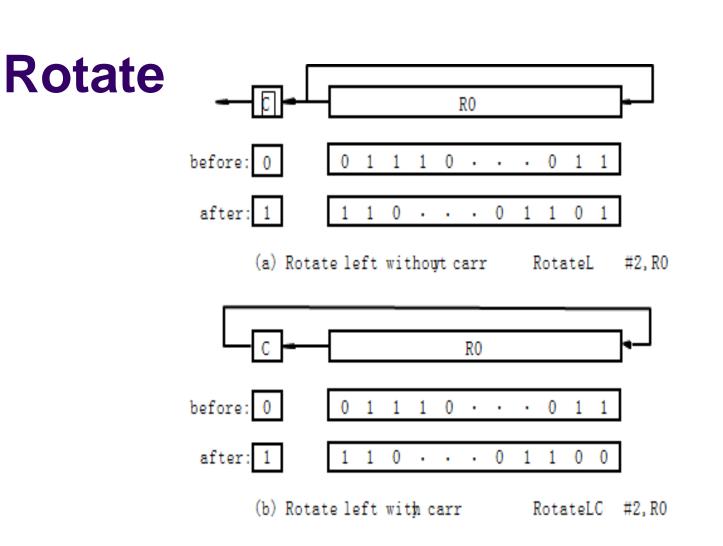

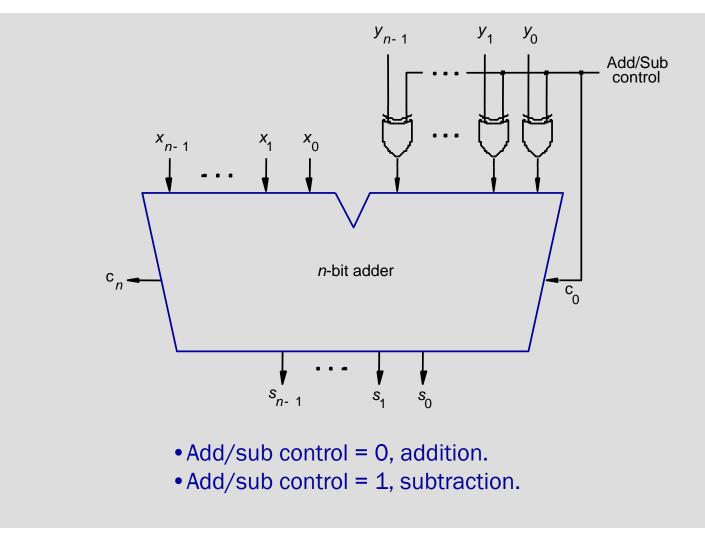

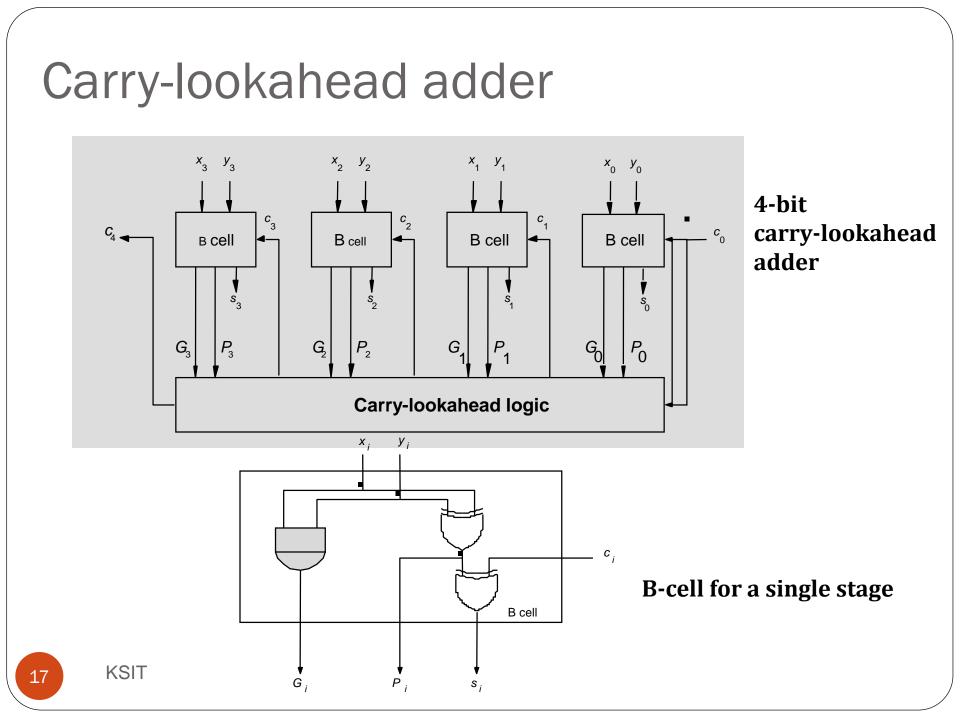

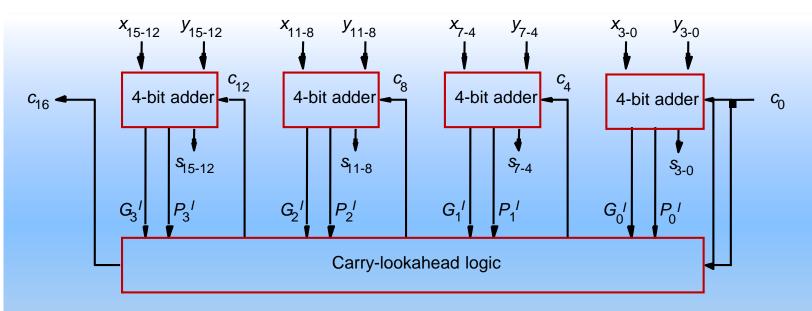

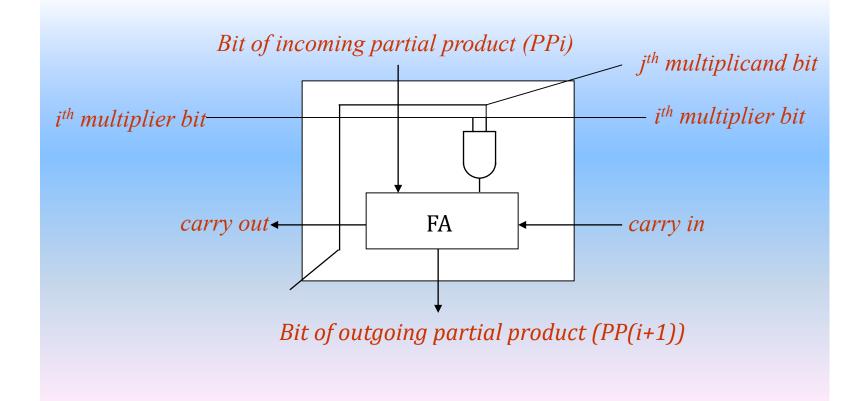

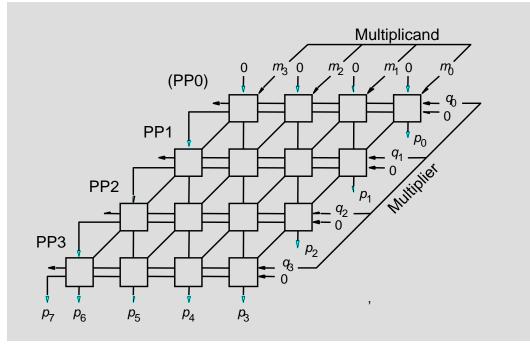

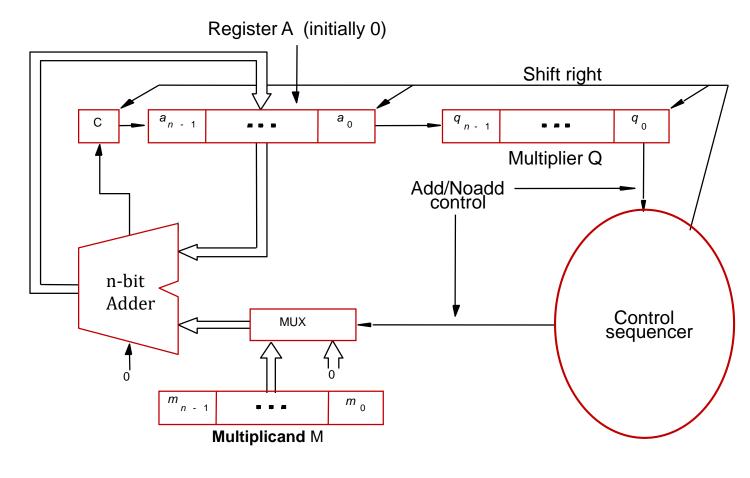

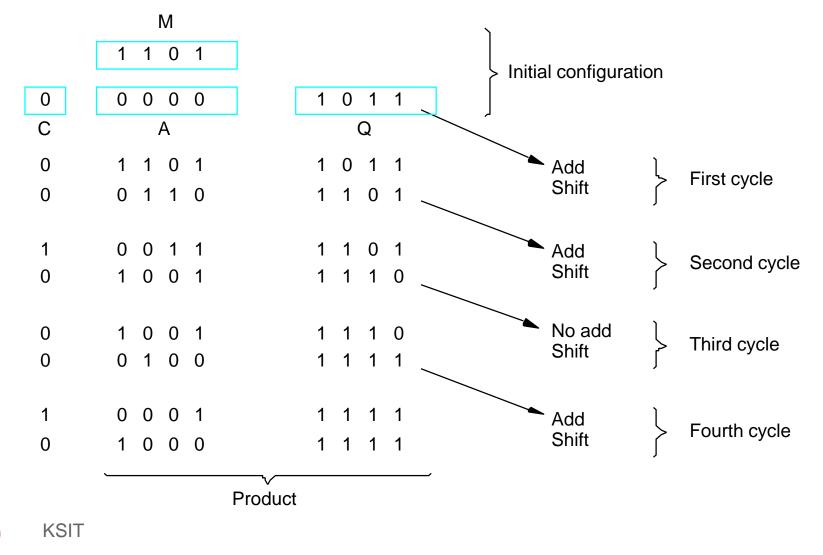

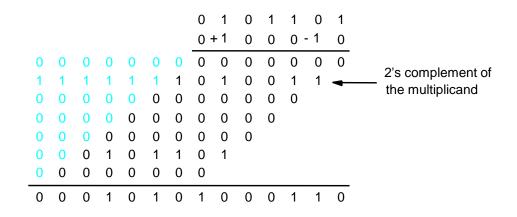

| Arithmetic: Numbers, Arithmetic Op<br>Signed Numbers, Design of Fast A<br>Operand Multiplication, Fast Multiplic<br>Text book 1: Chapter2-2.1, Chapter<br>RBT: L1, L2, L3                                                                                                                        | Adders, Multiplicati                                                                          | ion of Positive Numbers,                                                                               | iction of<br>, Signed | 08          |

| Module 5                                                                                                                                                                                                                                                                                         |                                                                                               |                                                                                                        |                       |             |

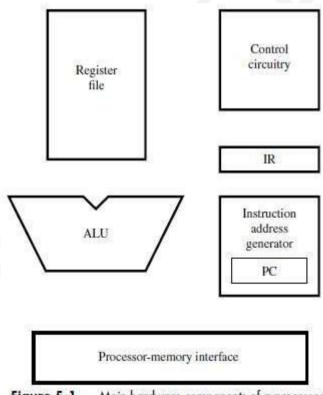

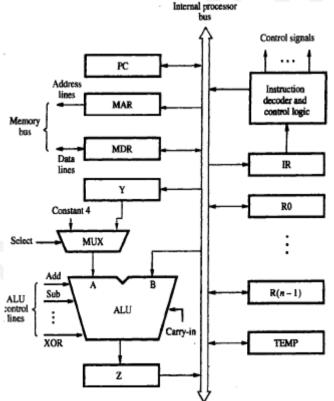

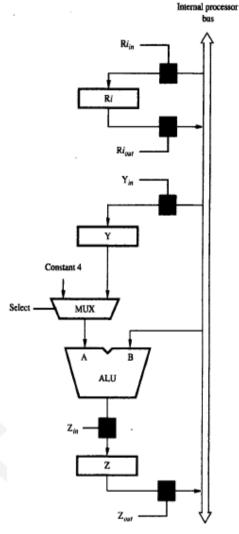

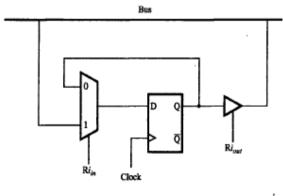

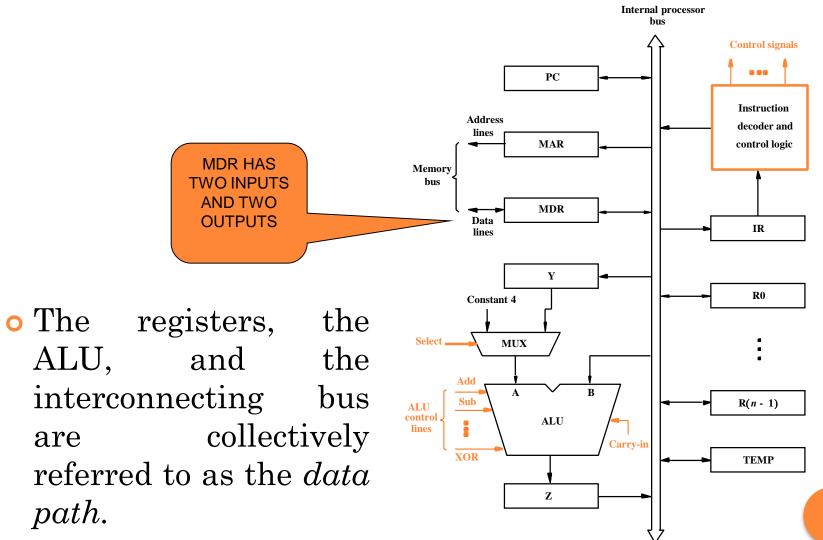

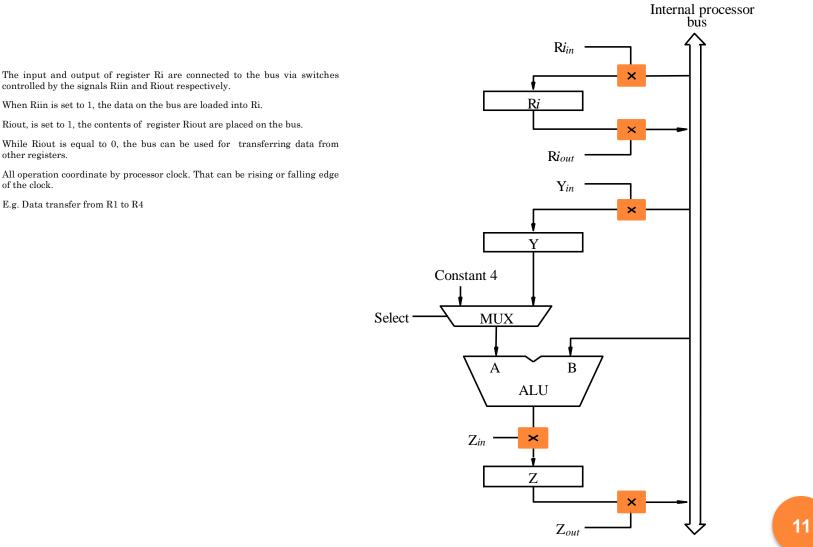

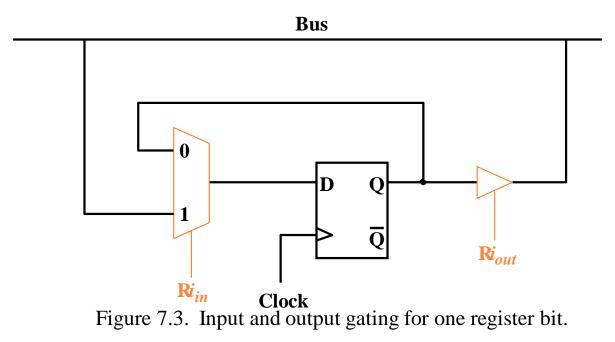

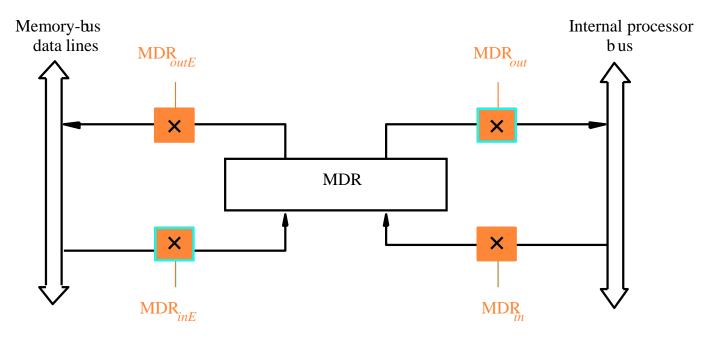

| Basic Processing Unit: Some Fundar<br>Multiple Bus Organization, Hard-wire<br>Pipelining: Basic concepts of pipelini<br>Text book 1: Chapter7, Chapter8 –                                                                                                                                        | d Control, Micro prong,                                                                       | kecution of a Complete Insogrammed Control.                                                            | truction,             | 08          |

| <b>RBT: L1, L2, L3</b><br><b>Course Outcomes:</b> The student will b                                                                                                                                                                                                                             | a able to :                                                                                   |                                                                                                        |                       |             |

|                                                                                                                                                                                                                                                                                                  |                                                                                               |                                                                                                        |                       |             |

.

- Demonstrate functioning of different sub systems, such as processor, Input/output, and memory. .

- Illustrate hardwired control and micro programmed control, pipelining, embedded and other ٠ computing systems.

• Design and analyse simple arithmetic and logical units.

#### **Question Paper Pattern:**

- The question paper will have ten questions. .

- Each full Question consisting of 20 marks

- There will be 2 full questions (with a maximum of four sub questions) from each module.

- Each full question will have sub questions covering all the topics under a module. •

- The students will have to answer 5 full questions, selecting one full question from each module. **Textbooks:**

1. Carl Hamacher, Zvonko Vranesic, Safwat Zaky, Computer Organization, 5th Edition, Tata McGraw Hill, 2002. (Listed topics only from Chapters 1, 2, 4, 5, 6, 7, 8, 9 and 12)

#### **Reference Books:**

William Stallings: Computer Organization & Architecture, 9th Edition, Pearson, 2015. 1.

Head of the Department

# Dept. of Computer Science & Engg. K.S. Institute of Technology Bengaluru -560 109

### KS INSTITUTE OF TECHNOLOGY BANGALORE

### **DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING**

- NAME OF THE STAFF : DEEPA .S.R

- SUBJECT CODE/NAME : 18CS34 / Computer Organization

- SEMESTER/YEAR : III / 'A'

- ACADEMIC YEAR : 2020-2021

| SI.<br>No. | Topic to be covered                                              | Mode of<br>Delivery | Teaching Aid               | No. of<br>Periods | Cumulative<br>No. of Periods | Proposed<br>Date |  |  |  |  |  |

|------------|------------------------------------------------------------------|---------------------|----------------------------|-------------------|------------------------------|------------------|--|--|--|--|--|

|            | MODULE 1:Basic Structure of Computers                            |                     |                            |                   |                              |                  |  |  |  |  |  |

| 1          | Introduction to CO                                               | L+D                 | PPT using<br>Zoom Platform | 1                 | 1                            | 3/9/2020         |  |  |  |  |  |

| 2          | Basic Operational Concepts                                       | L+D                 | PPT using<br>Zoom Platform | 1                 | 2                            | 4/9/2020         |  |  |  |  |  |

| 3          | Bus Structures, Performance – Processor Clock,                   | L+D                 | PPT using<br>Zoom Platform | 1                 | 3                            | 5/9/2020         |  |  |  |  |  |

| 4          | Basic Performance Equation, Clock Rate                           | L+ D                | PPT using<br>Zoom Platform | 1                 | 4                            | 7/9/2020         |  |  |  |  |  |

| 5          | Performance Measurement                                          | L+ D                | PPT using<br>Zoom Platform | 1                 | 5                            | 10/9/2020        |  |  |  |  |  |

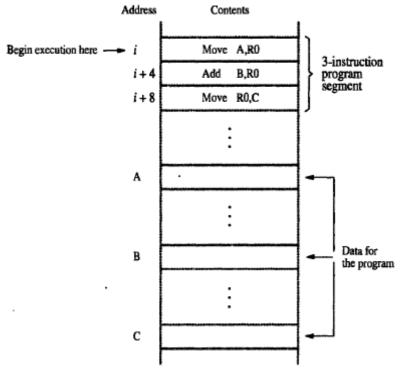

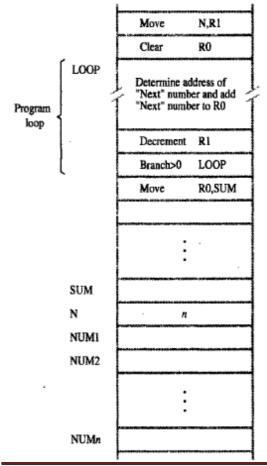

| 6          | Machine Instructions and Programs: Memory Location and Addresses | L+ D                | PPT using<br>Zoom Platform | 1                 | 6                            | 11/9/2020        |  |  |  |  |  |

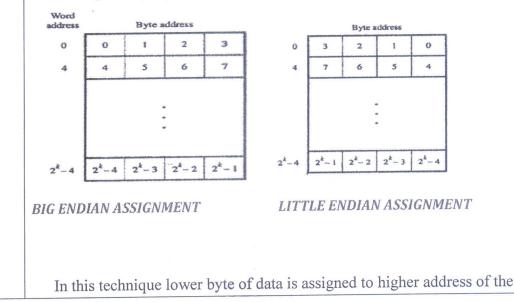

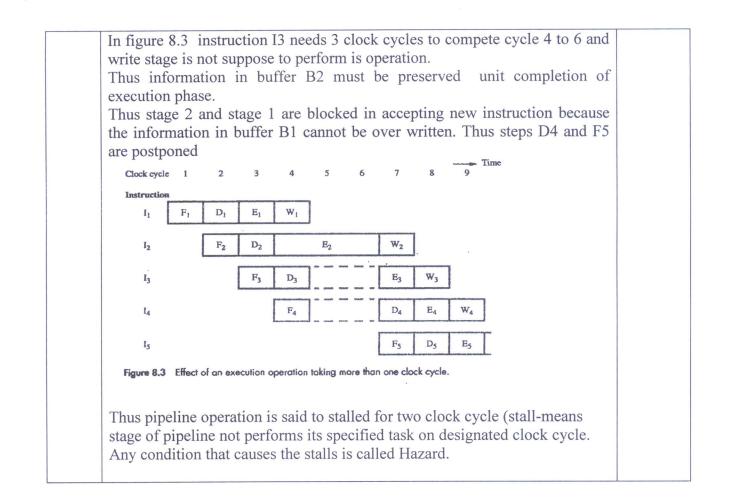

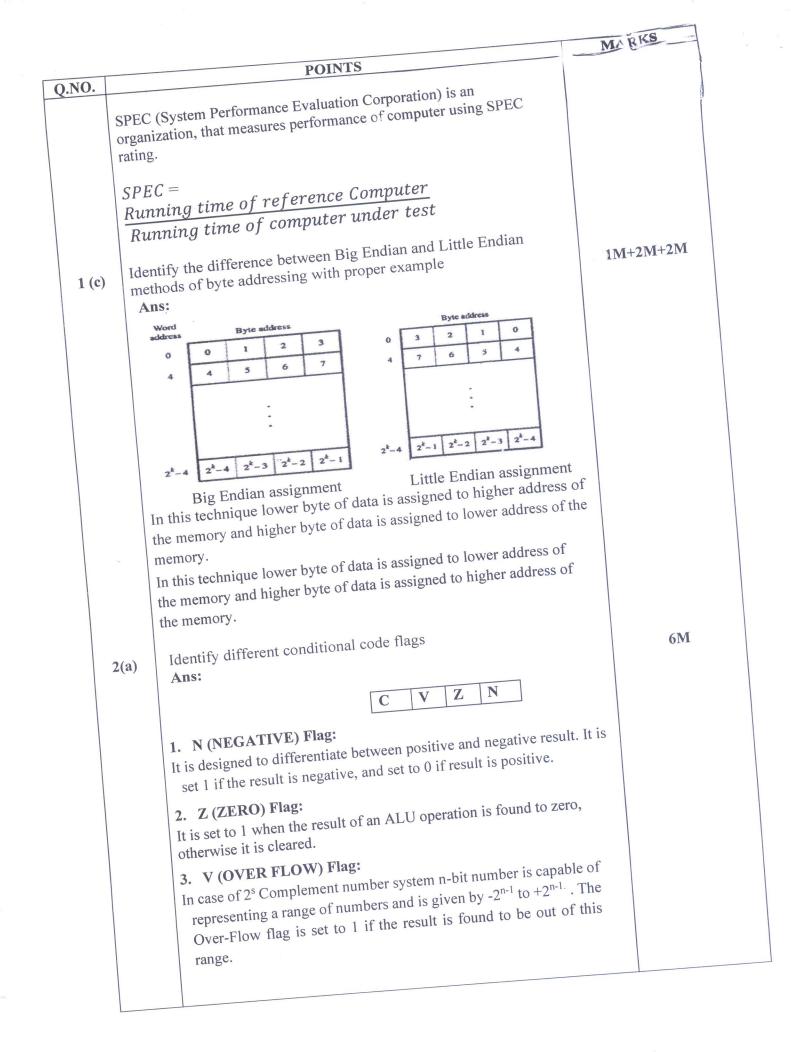

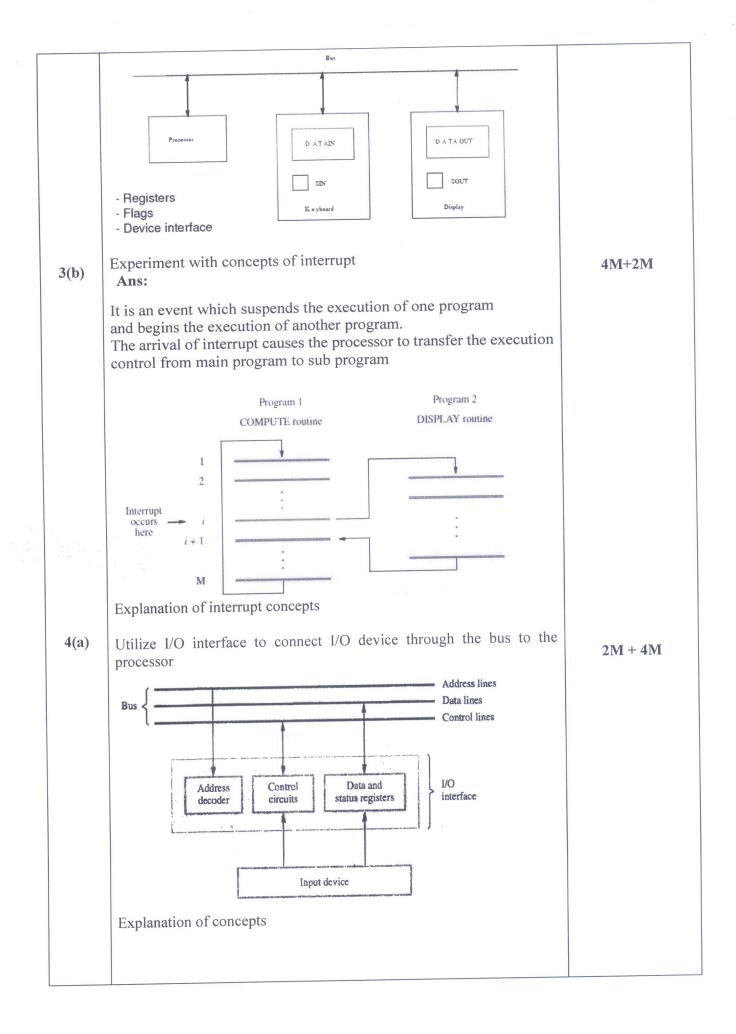

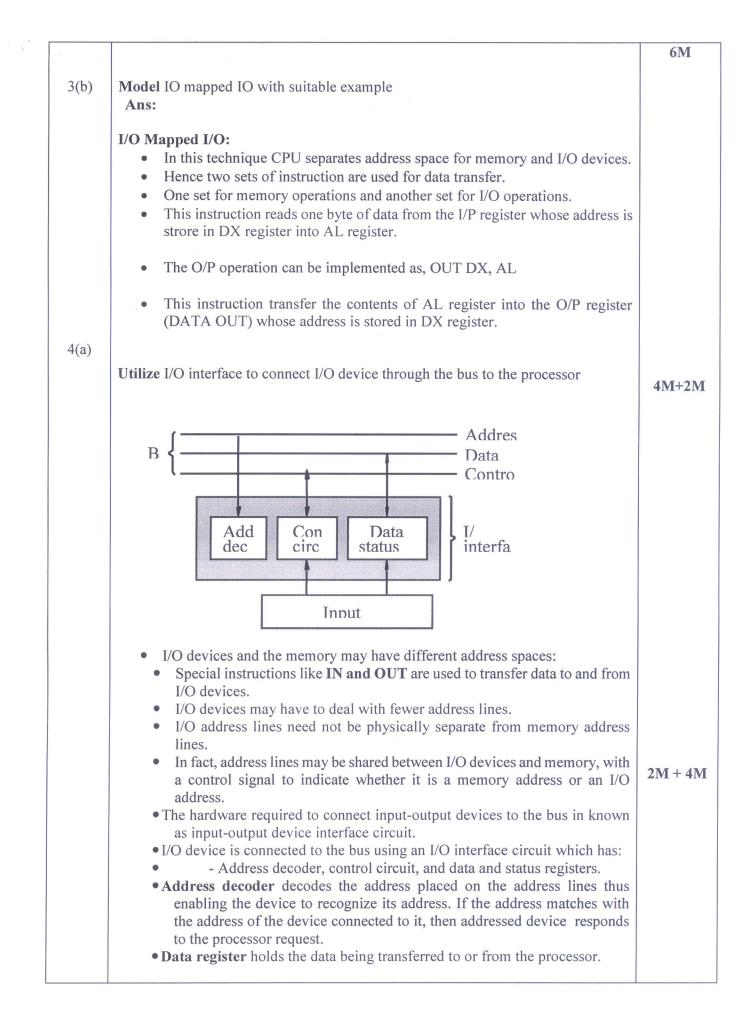

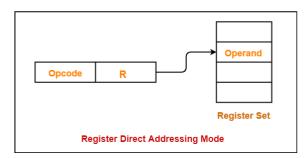

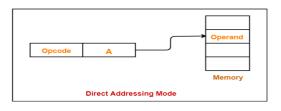

| 7          | Memory Operations, Instructions and Instruction Sequencing,      | L+D                 | PPT using<br>Zoom Platform | 1                 | 7                            | 12/9/2020        |  |  |  |  |  |